互连总线的产品生命周期(上)

可携式刺激源标准(PSS)是最新的业界标准,其用来规范测试意图与行为,让测试刺激源可重复套用到不同的目标平台。PSS不仅改变系统单芯片(SoC)传统的确认与验证方法,也带来了许多优点以及衍生不少挑战。本文探讨这些流程演变,以及从SystemC效能分析探索互连总线架构的生命周期,藉以透过通用型PSS流量产生器进行确认与验证。

随着设计要求日趋复杂,验证技巧与方法也随之不断演进。可携式刺激源标准(PSS)是演进的最新产物,它的目的是因应测试可移植性的挑战。新型PSS允许用户建立测试意图,藉以重复套用到不同的目标平台。除了可移植性之外,PSS验证技巧还提供多方面的价值,包括视觉测试代表性、限制设定、数据流随机性及更高的测试质量。

后续的流程演变,包括SoC确认与验证流程,以及采用PSS技巧,这对了解其冲击相当重要。本文探讨这些演变,提出一项互连总线架构的案例研究,进行SystemC效能分析解说确认与验证过程。

设计特点

随着设计复杂度持续攀升,包括SystemC模型分析、架构探索及高阶合成(HLS)等流程演进,在传统设计与整合流程中越来越常见。这些流程演变衍生出许多要求,其中包括检查是否符合系统设计的要求。参与这些流程的团队会用使用不同类型的平台与语言来推动这些演变。尽管存在这些差异,后续流程的基本规格都是相同,因此导致出现许多重复工作。

架构研发团队针对使用SystemC与架构探索与TLM模型分析法建立虚拟平台,藉以执行架构探索与软件开发。组件设计团队则会在模块层级设计Verilog组件并加以整合,再以人工或自动化程序建立系统。

IP层级的验证通常采用UVM验证在IP层级进行,而在系统层级方面则使用C语言与以UVM方法。UVM环境让检查组件从IP层级到系统层级都能轻易重复使用,但测试刺激源通常会重新撰写,藉以在顶层UVM环境运行,或使用C语言撰写藉以在芯片层级的处理器上运行。建立测试组件验证startup类别/组态以及模块的基本模式运行,在实际芯片测试过程中会重复执行,因为测试平台需要新测试程序或是必须在评估板上运行。因此软件团队必须针对客户的接口撰写驱动程序。

当各团队使用不同语言与技巧执行重复性工作,经常导致出现假性bug通报,并大幅拖慢上市时程。因此业界需要更好的解决方案,让整个项目所有撰写测试码的人员都用一套共通语言,并让大部分的功能验证测试在横向与纵向方面都能无缝重复利用。这种不同以往的方法正是PSS验证技巧带来的优势。

PSS定义出新的测试撰写语言,它将让业界能自动产生测试程序,运用单一测试源套用到不同平台。除了横向的可重复使用性(模拟、仿真、机板层级、测试器等),新语言还允许测试程序的纵向重复使用性。在IP层级开发的测试程序在SoC层级上可更轻易整合与重复使用。

可携式刺激源在更高的抽象层上运行,它和目标平台的种类完全独立。这里的目标平台可以是UVM式验证环境、C/C++与SoC型环境、C语言与PythonR芯片后评估平台等。

PSS应用提供建立通用型应用的卓越机会,用来在各种层级进行检验与测试意图。在多处理器SoC中使用互连总线,也会出现类似的机会。我们需要在不同层级检验与评估功能及效能。

由于必须根据SoC的特定需求明智挑选互连总线架构,因此需要进行初期效能分析,这方面可使用系统模型分析(通常以C/SystemC语言撰写)。这方面必须建立可检验系统模型的测试程序。选好组态以及产生RTL之后,就需要执行IP层级的检验。这方面需要执行UVM验证以及UBM程序。因此,产生的RTL除了在SoC系统层级进行整合,还需执行在SoC层级的验证。这方面通常是撰写C/C++执行程序的验证与确认

所有这些互连验证应用都可采用PS技巧建立可重复使用的测试程序。要完成这种工作,会针对通用流量产生器建立PSS模型,这种模型会针对不同主控器(master)数量建立不同的读取与写入模式。流量产生器会针对每种主控器产生不同分布的流量,藉以仿真(emulated)高速与慢速的主控器。

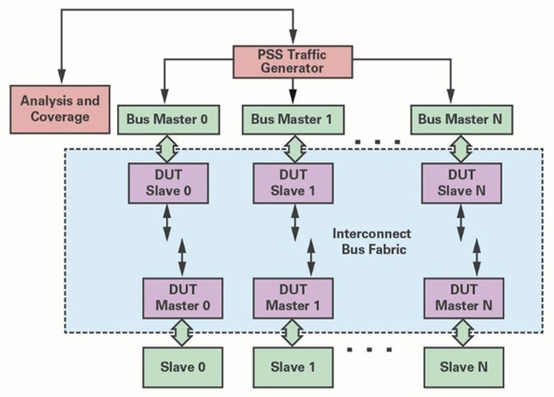

此外,我们还能单独控制哪个主控器在什么频率下产生流量,以及建立连续(back-to-back)与延迟的交易。图1显示运用PSS流量产生器的流程。紫色模块代表含有通用从属端与主控器的互连总线,绿色模块则代表RTL,或是驱动总线交易的行为模型。PSS式流量产生器(粉红色)整合与控制这些模块,用来驱动与收集交易。流量产生器除了应付不同种类的流量产生需求,还针对SystemC应用、UVM、以及C语言测试等各种目标建立测试。每种程序在整合与测试方面的处理方式都不相同,我们会在后面详细介绍。

图1 : 互连总线在效能分析与验证的PSS流程

互连总线的SystemC效能分析

互连总线的效能分析是在SoC开发流程中尽可能在初期对系统效能与功率进行定量量测。互连总线的效能必须针对各种类型应用、平台、以及互连组态(拓扑、功能、组态)进行评估。过程中涉及搜集需求、建立规格、归纳出这些规格、最终转化为符合效能/功率/面积要求的内聚设计。迭代程序在设计过程中持续进行。每次迭代都必须搜集规格,并和设计与研发团队进行交流。

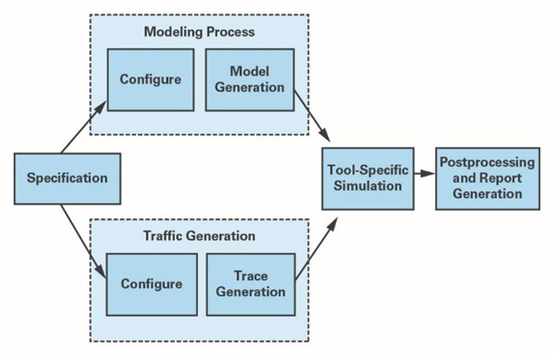

这方面是采用SystemC代表TLM模型,藉以反映SoC规格,这些规格可用来精准预测系统行为。图2显示这种流程,一开始是从设定工具开始,工具用来产生SystemC模型。这些模型是工具套件的一部分,我们设定套件使其配合设计的各项需求。它可用来产生精准周期,或针对AMBA主控器与从属端、频率产生器、以及刺激源建立粗略模型。产生模型后,必须撰写这个层级的流量模式,可选择以人工撰写或使用自动程序文件将规格转换成实际仿真与产生结果。之后运用特定仿真器来仿真模型,提供解决方案进行效能的量化分析。

图2 : 使用SystemC建模法分析效能

尽管已有模型与分析工具,但使用这些工具来处理多项候选设计,耗费时间会相当可观。使用描述式(scripts)来产生流量虽然可以提供某些类型的流量模式,但繁复的情境产生程序仍会是一项问题。此外,由于各项模拟非常费时,因此在模拟结束后进行分析,势必会增加试验的数量,藉以达到预期的数据。

另外,再加上设计以及效能建模程序中花在规格管理的时间,可看出我们需要更趋自动化的流程,这种流程应以单一来源做为起点。PSS技巧是因应这些挑战的有效方法。PSS工具的随机化机制,一开始是抽象描述DUT高阶状态的合法交易,然后自动列举覆盖测试所需的最小测试组合,涵盖整个状态空间的各路径。

PSS工具的覆盖机制能衡量在特定状态空间中已覆盖多少状态。这种能力让系统在产生任何刺激源之前就能量测覆盖状况,因此能节省执行此程序的时间。PSS覆盖数据让用户能检视横向(transverse)路径以及产生测试程序,藉以覆盖最大长度的图像。因此能以远低于一般受限随机验证程序耗费的周期,藉以达到更高的覆盖率。

PSS工具亦提供测试意图的视觉代表,藉以提供更好的情境图像表征。指向式测试涵盖特定的测试条件,可透过这项功能轻易转移。此外它亦能限制某些条件组合,因此能针对特定功能组合建立受限制随机情境。PSS技巧基本上能维持如图2所示的流程,但路线产生程序会有明显的改变。

流量产生器的核心是通用PSS模型,模型容纳的算法负责产生不同类型的流量模式。这是刺激源与测试情境的单一表征方式。这种模型可用多种方法进行设定,产生的测试程序可包含许多可能产生流量组合的其中一项。它包含三个部分:

1.执行模块(Exec blocks)

执行模块是从外部程序代码撷取的陈述,这些陈述位于目标平台的PSS包装函式(wrapper)。对于SystemC程序,客制化程序代码会执行不同类型的读取与写入作业,将数据写入底层环境。在UVM SV部分,它也有衍生至工具提供宏(收发器产生)的逻辑,并透过PLI系统呼叫来和SV世界进行互动。另外还有一个部分(C语言产生)能执行转译与运用C语言进行互动,在不同平台之间无缝重复备使用。

2.PSS模型 :

根据整组规格建立的实际使用案例模型。它包含的功能组合,涵盖执行一系列动作的高阶程序。流量产生器包含不同的算法组合,代表各种简单与复合动作。这些功能最终会呼叫执行模块的函式,用来在SV端执行指令。

3.PSS组态:

模型一般需要特定信息来产生特定测试。这些信息和验证有关连,像是AMBA主控器、从属端、主控器种类、来源与目的地地址、存取种类、平均带宽、突发大小、数据量、频率、以及带宽需求等。这项信息必须取自规范,藉以产生测试意图的正确表征。

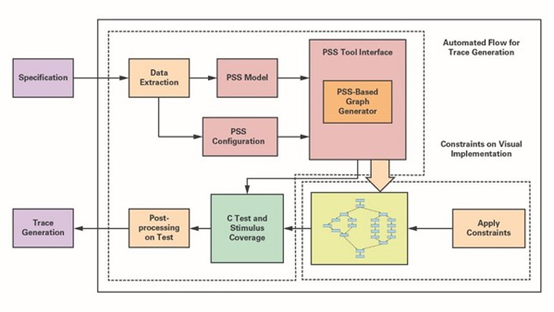

图3 代表PSS流量模式产生流程,最先是从剖析规格开始。Python语言撰写的描述式用来剖析电子表格格式的规格,撷取出特定格式的数据可透过PSS模型与组态加以读取。之后利用PSS工具剖析PSS模型与组态,产生测试意图的视觉表征。

图3 : 运用PSS流程产生流量模式

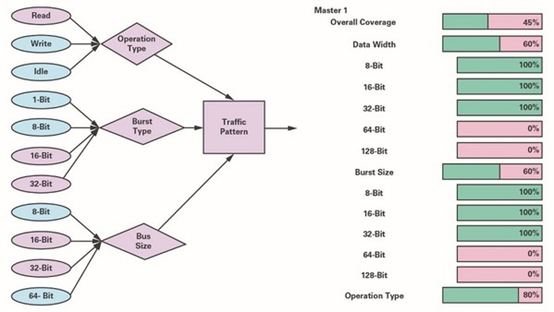

图4显示一部分的测试意图视觉表征。图中有代表写入与读取作业的条件、单一或Burst Mode,以及不同总线大小,可加以控制以产生不同类型的流量模式。紫色的部分代表能转移(transverse)的条件,蓝色则属于不被纳入考虑的部分。这种安排能协助用户图像化,以及限制部分的流量。

图4 : 测试意图与PSS覆盖范围的视觉代表图

倘若使用者没有加入限制条件,PSS工具会随机选取某些组态,然后建立受限制的随机测试。在这个阶段还可以搜集工具覆盖范围,以及提早分析完整性(completeness)。工具执行的覆盖分析方法,可在工具产生测试中衡量测试意图的覆盖状况。图4代表PSS工具产生的PSS覆盖范围。粉红色模块代表未覆盖的条件,绿色则代表已覆盖的条件。使用者可观察这种代表图,针对未覆盖的条件建立测试。

在产生测试程序后,再执行后置处理描述式以建立流量模式,这种模式兼容于效能分析仿真工具的客制化格式。接着下一步是执行模拟并产生流量,产生大量的未处理数据,这些数据之后经过处理,汇整出不同标准的数据与视觉图像,对结果进行有效分析。

表1显示几个例子,这些产生报告内含各项参数,用来针对含有多个主控器与从属端的SoC对其除错器进行效能分析,再对获得的数据进行计算。这种分析可以是一(主控器)对一(从属端)与多对一模拟(称为实验),根据平台规格产生结果。系统是根据频率频率的静态分析以及平台规格定义的数据宽度产生这些实验,设定用来让系统在理论最高带宽运行。

一般而言,PSS流量允许更好地配置随机情境,锁定特定的总线组态。此外,测试意图的视觉表征有助于产生更好的限制。可视化覆盖促成更好的流量模式,因此在特定的主控器-从属端系统中,只需较少次数的迭代就能达到最高的可行带宽。

表1. 运用系统解决方案PSS仿真的数据收集

实验 ID | 主控器 | 从属端 | 方向 | 平均仿真带宽 | 平均静态带宽 | 平均仿真延迟 |

5000 | Core | SMMR | Read | 1199.72 | 6000 | 24 |

5001 | Core | SMMR | Write | 999.79 | 6000 | 24 |

5002 | Core | L2 mem | Write | 99.92 | 100 | 24 |

5003 | Core | L2 mem | Read | 99.92 | 100 | 21.34 |

我们看到实质的改善,包括运用PSS技巧,在经过次数的迭代后就能达到最高平均仿真带宽,进而节省仿真周期与分析时间。藉由减少建立互连架构效能模型所需的工作量,以及在统一规格下的单一真值来源(single source of truth),任何重新设定时间都能大幅缩短。这样的流程让我们能探索许多设计候选方案,然后选用其中一项执行时序收敛以及RTL流程。

(本文作者Gaurav Bhatnagar、Courtney Fricano为ADI主任工程师)

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码