基于双向可控硅隔离型延时可控电路的实现方法

3 相关参数分析

3. 1 电容降压

将交流电转换为低压直流的常规方法是采用变压器降压后再整流滤波。文中,为简化电路设计,提高效率,减小体积,降低成本,该电路采用电容降压方式。图1 中电容C4 的作用为降压,电容的选取由所需要通过电容的电流IC 的大小决定:

经测量,该电路电流在70 mA 左右,电容所产生的容抗约为3 180 Ω ,因此电容C4 取1 μF.当220 V 的交流电压加在电容器的两端,虽然流过电容的电流有70 mA ,但在电容器上并不产生功耗,因为如果电容是一个理想电容,则流过电容的电流为虚部电流,它所作的功为无功功率。同时为保证C4 可靠工作, 其耐压选择应大于2 倍的电源电压。

R3 为关断电源后电容C4 的电荷泄放电阻, 其选择必须保证在要求的时间内泄放掉C4 上的电荷。

用电容降压时,必须考虑一个重要问题,就是在合上电源的瞬间,有可能是220 V 交流电的正或负半周的峰峰值,此时瞬间电流会很大,虽然该电流持续时间极短,但足以烧毁稳压管。解决这一问题有2 种方法,一是在电路中串联电阻,缺点是消耗功率,二是用适当电压的P6 KE 瞬态抑制二极管,缺点是价格稍贵。

3. 2 延时时间

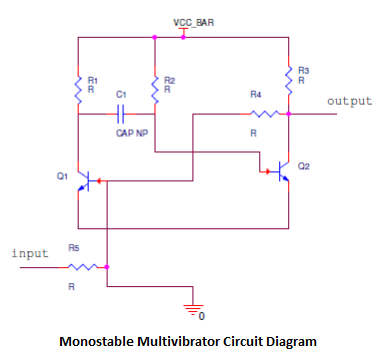

本文所介绍的电路,采用555 定时器作为延时计时器,延时时间由电位器R1 和电容C1 决定, 延长的时间TW 为:

4 仿真及实验

4. 1 仿真波形

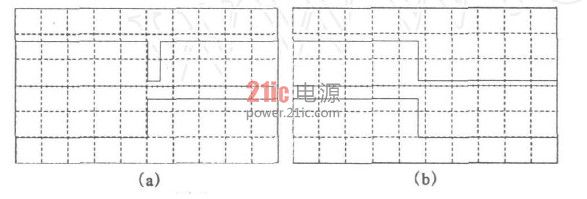

Multisim 提供了庞大的元件数据库,并提供原理图输入接口、全部的数模Spice 仿真功能、V HDL/ Verilog 设计接口与仿真功能、FPGA/CPLD 综合、RF 设计能力和后处理功能,特别适用于复杂电路仿真。本电路采用Multisim 建立仿真电路,其电路仿真波形如图2 所示。

图2a 纵坐标为10 V/ 格,横坐标为100μs/ 格,由上至下两条波形分别是:555 定时器U3 第2 管脚触发波形;555 定时器U3 第3 管脚输出波形。这里将触发器U8 内部第一个触发器的暂态时间设定为50μs.图2b 纵坐标为10 V/ 格,横坐标为100 ms/格,由上至下2 条波形分别是:555 定时器U3 延时时间结束输出波形;单稳态触发器U8 第11 管脚触发波形。这里将U8 内部第2 个触发器的暂态时间设定为100 ms ,以确保光耦合驱动器U4 、可控硅D1 完全关断。

图2 电路触发仿真波形

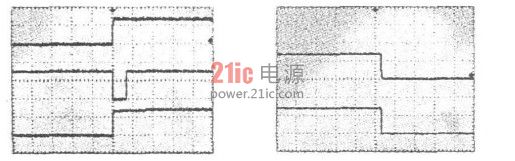

4. 2 实验波形

用Tek TDS2014 可存储示波器测得的输出波形如图3 所示,图3a 第1 条波形为开关K1 置于触点2 时单稳态触发器U8 第4 管脚触发波形,其余波形与仿真波形为一一对应关系(图3a 横坐标为100μs/ 格,纵坐标为10 V/ 格;图3b 横坐标为100ms/ 格,纵坐标为10 V/ 格) .由图3 实验输出结果看出,电路触发和延时与理论分析和仿真结果一致,该电路工作性能良好稳定。

图3 电路触发实验波形

5 结束语

介绍了一种应用双向可控硅,单稳态触发器和555 定时器的延时电路,通过数学分析和实验结果得到以下结论:

a. 能耗低。电路工作时,能耗在2 W 左右。

b. 隔离。延时结束后,电路、用电器与电源完全隔离。

c. 延长时间调节范围宽。通过调节电位器,延长时间从0 到数小时。

d. 可靠性高。由于使用了双向可控硅,电路可达到无触点、寿命高、电磁干扰小的效果。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码