使嵌入式 STT MRAM 磁隧道结阵列的加工成为可能

半导体产业正在迎来下一代存储器技术的新纪元,几大主要变化趋势正在成形。这其中包括磁性随机存储器 (MRAM) 的出现。我将在几篇相关文章中介绍推动MRAM 得以采用的背景,重点说明初始阶段面临的一些挑战,并探讨实现 STT MRAM 商业可行性的进展。

应用材料公司为实现 STT MRAM 的制造提供了多项重要创新,包括基于Endura® 平台上的PVD创新以及特别的蚀刻技术。利用这些新技术并借助梅丹技术中心的设施来加工并测试器件阵列,我们验证了 STT MRAM 的性能和可扩展性。

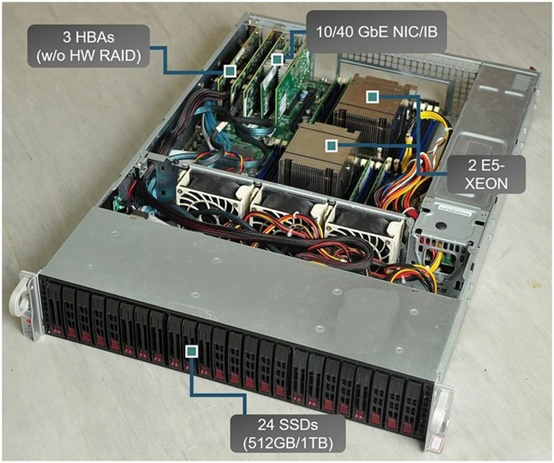

如今,除了逻辑元件和其他专用电路元件外,典型的微控制器 (MCU) 包括用作工作存储器的 SRAM 和用作储存存储器的闪存。当前业界遇到的闪存问题是,要将浮栅 (FG) 的制造工艺对逻辑门性能的影响降到最低(图 1)。为此,制造商通常会使用多达 10 个的额外掩膜层,这必然会增加其复杂性和成本。在 <28nm 的节点, 逻辑部分的工艺将迁移到高 k 栅介质/金属栅极(HKMG),由于 HKMG 的热预算有限,将导致工艺集成更为复杂。

图 1:带闪存(左)和 STT MRAM(右)的 MCU 集成方案

另一方面,在后端工艺 (BEOL) 中集成自旋转移矩 MRAM (STT MRAM) 较为容易,只需要3个额外的掩膜(图 1)。此外,与 STT MRAM 相比,闪存的能耗较大。STT MRAM 具有前景的特性(快速、非易失性、低功耗和在低温下易于实现 BEOL 集成)使大多数主要逻辑和存储器厂商开始逐步开发 STT MRAM 技术。除 MCU 外,由于 STT MRAM 可以实现相比于 SRAM 更高的密度,STT MRAM也正在被开发用于取代 SRAM,用作 <10nm 节点的最后级缓存。

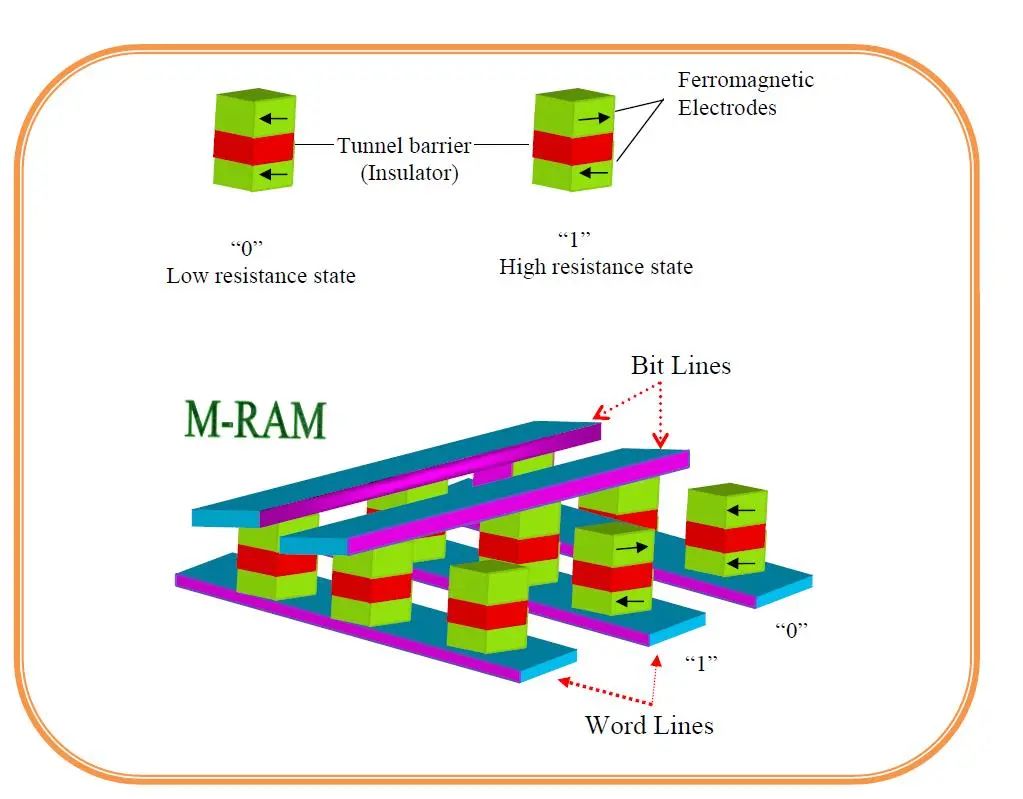

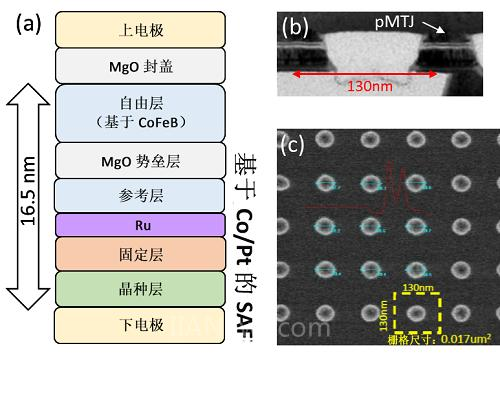

STT MRAM 的每个存储单元都由磁隧道结 (MTJ) 组成,其最基本的形式是由夹在两个磁性薄膜(约 10-30Å 厚的 CoFeB)间的薄介质隧穿势垒膜(约 10Å 厚的 MgO)组成。在 MTJ 堆叠中实际有许多额外的薄膜层(参见示例中的图 2a),并且自 2007 年以来已作为硬盘驱动器 (HDD) 中的读取传感器进行制造。

图 2:(a) pMTJ 堆叠细节、(b) 和 (c) 所示为 pMTJ 阵列的横截面图和俯视图

但是,针对 HDD 中单独的 MTJ 器件与 STT MRAM 中垂直 MTJ (pMTJ) 器件阵列的要求是完全不同的。关于pMTJ 薄膜堆叠层沉积和蚀刻工艺设备的创新对于制造密度/性能有竞争力的 STT MRAM 至关重要。此外,即将生产 STT MRAM 的存储器制造厂晶圆初始的产量比 HDD 磁头制造厂高 10-20 倍,因此在设计设备时,设备的正常运行时间是要考虑的关键因素。

应用材料公司已在公司的 Endura 平台上针对 pMTJ 堆叠层沉积(具有可控微观结构、清洁界面和sub-Å 精度的多层薄膜)开发出多阴极 PVD 室以及各类原位热处理室。此外,还针对蚀刻 pMTJ 阵列开发了用于密集阵列中非易失性磁性材料的特别蚀刻技术。[1]

为了评估 pMTJ 沉积和蚀刻设备的性能,在梅丹技术中心设计并制造了 1R pMTJ 阵列测试芯片。最小存储单元尺寸 130nm x 130nm(图 2)等同于 28nm 节点处的 22F2,相当于约 1Gb 密度。这些测试芯片已在高通公司进行过电性分析,结果也在2015和2016的国际电子元件会议(IEDM)中共同发表。[2, 3]下列段落中讨论的这些结果,着重关注使用 Endura PVD 系统和特别蚀刻技术制造的 pMTJ 阵列性能。

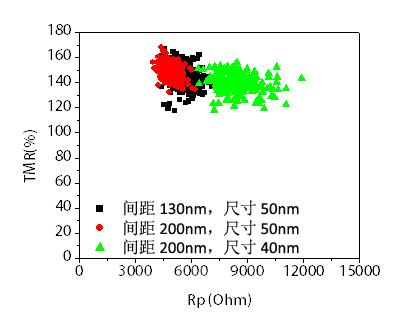

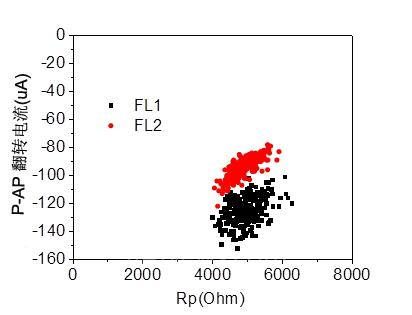

一个关键的性能指标是蚀刻后 MTJ 阵列的 TMR%(隧道磁电阻)。对于间距为 130nm 和 50nm 直径的 pMTJ 阵列,平均 TMR 约为 150%(图 3)。电阻(RP)的西格玛/平均值 <8%。这两个数值都表明蚀刻过程中的蚀刻损伤极小。通过优化 pMTJ 堆叠层中的自由层 (FL) 材料,在阵列中可获得低至约 90uA 的P-AP 翻转电流(35ns 翻转脉冲)(图 4)。

图 3:采用不同阵列间距和 CD 的 TMR 百分比图

图 4:通过自由层 (FL) 优化来降低翻转电流

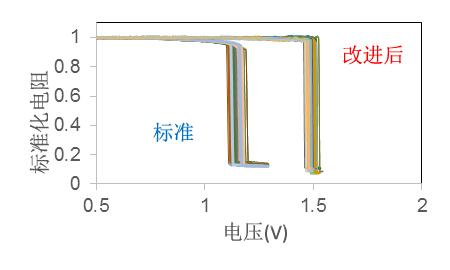

最后,通过优化 MgO 沉积室的设备硬件设计,如图 5 所示,可使约 10Å MgO 隧道势垒层的击穿电压从约 1.2V(标准)显著提高到约 1.5V(改进后)。如我们的工作中所演示,这对于提高耐用性至 >1015 个写入周期至关重要。[3]我将在下一篇博客中进一步探讨这个问题。

图 5:通过工艺和设备硬件优化实现 MgO VBD 改进

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码