基于FPGA的34位串行编码设计

新型舰艇或航空系统中所装电子设备数量较多,布局紧凑,易造成系统内部电磁干扰,普通数字信号不能够满足可靠传输的要求,对普通串行码进行调制后传输信息,可使信号的抗干扰性能大大增加。RS232、RS422、RS485以及ARINC429等都是电子设备中常用的串行数据传输标准。

某专用接口装置采用一种点对点的34位串行编码数据传输标准,34位串行编码经耦合变压器调制后进行信息传输,能够在恶劣的电磁环境下可靠传输数据。为实现对该接口装置的测试,研制了针对该装置的检测设备,可用于该装置接口功能的检查和故障排除。

与其他常用的串行编码(如异步串行码等)相比,专用接口装置所采用的34位串行编码的格式有所不同,常用串行编码的收发大都有专用的芯片来完成,而该类型的34位串行编码没有相应的号用收发芯片直接应用,因此在该专用接口装置检测设备研制中,基于FPGA芯片设计了34位串行编码信号的检测电路,实现了34位串行编码信号的可靠收发。

1 34位串行编码的格式

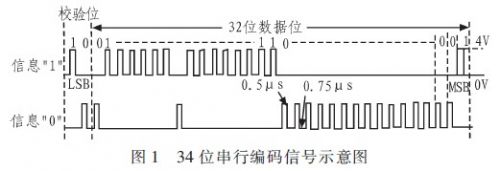

专用接口装置收发信息使用的34位串行编码为归零码,解决了数位难以分辨的问题,接收端可以利用编码自身携带的时钟信息。34位串行编码的收发采用耦合变压器方式,加大了高电平和低电平之间的电位差,有利于提高传输的可靠性。串行编码信号高低电平幅度分别为4 V和0 V,一个码位的高电平脉冲宽度为0.5μs,归零时间为0.75μs,传输速率为800 kbps。为进一步增强通信的可靠性,串行数据采用双线传输。传输信息时,信息“1”和信息“0”分别由两个电缆传输,称为信息“1”线和信息“0”线。

对于信息“1”线,数据位为“1”时,发送一个归零脉冲,数据位为“0”时,发送低电平;信息“0”线则正好相反,数据位为“0”时,发送一个归零脉冲,数据位为“1”时,发送低电平。连续发送两个34位串行数据时,时间间隔最短不得小于4个归零脉冲周期。

34位串行编码的前两位为校验位,后32位为数据位,均是先传输低位。校验位的计算方法为:32位串行数据经过模3运算后,取反码的值即为校验位。以图1说明34位串行码的格式。图1中要传输的32位数据为0X8000FF7E,该数值经过模3运算后,值为0X10,该值取反码后为0x01,即是校验位。

2 34位串行编码收发模块的设计与实现

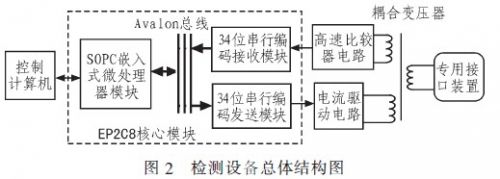

专用接口装置的检测设备能够实现34位串行编码的收发,用以验证专用装置的接口功能是否正常,检测设备的总体结构图见图2。实现34位串行编码的可靠收发是研制检测设备的关键技术。在分析34位串行编码格式的基础上,基于FPGA芯片EP2C8研制了核心模块,模块可以接收上位控制计算机的命令,完成34位串行编码数据的收发。核心模块前端的信号调理电路包括发送信号时的电流驱动电路、接收信号时的高速比较器电路以及双耦合变乐器。

实现34位串行编码的收发需要设计34位串行码的同步时钟提取电路,通过移位寄存器进行收发,发送数据校验位的产生和接收数据校验位的验证需要用到运算模块,电路设计比较复杂,所需硬件较多,而且由于34位编码传输速率较高,为了保证收发可靠、不漏码,从功能和实现成本上考虑,在电路设计上,采用了大规模可编程逻辑芯片实现34位串行编码信号的接收和发送。所用FPGA芯片为Altera公司的CvcloneⅡ系列中的EP2C8,该芯片内核电压为1.2 V,输入输出口为3.3 V逻辑电平,功耗很低。核心模块设计采用原理图输入和VHDL语言相结合的方式,利用OuartusⅡ软件和SignalTap功能进行逻辑电路的开发和调试。

2.1 34位串行编码的接收

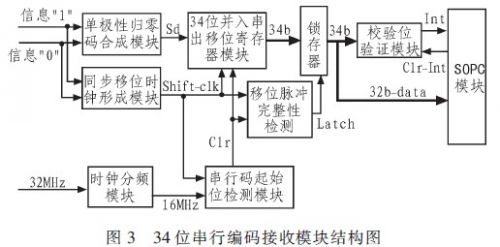

34位串行编码接收模块结构图见图3。在接收34位串行码时,首先要对接收信号进行解调,来自耦合变压器的34位串行码经过高速比较器CMP401电路进行整形处理,转变成普通数字电路容易处理的单极性归零码。

接收34位串行编码信息需利用串行码自身携带的时钟信息,将信息“1”和信息“0”的脉冲相或,即可得到移位时钟(Shift-clk)。接收模块各节点信号时序图如图4所示。

在单极性归零码合成模块中,信息“1”和信息“0”分别送到D触发器的预置端和清零端,经过D触发器处理后,产生单极性归零码信号(Sd)。将单极性归零码信号送入到34位串入并出移位寄存器模块中,在移位时钟的作用下,单极性归零码信号在串入并出移位寄存器模块内逐位移动,形成34位并行码,并由锁存脉冲(Latch)锁存并行数据,校验位验证模块对并行数据进行模3校验位验证,当校验位正确时,产生确认脉冲,作为嵌入式控制器SPOC模块的中断信号,SOPC模块响应中断并执行中断服务程序,读出并行数据,存储在存储器中。

串入并出移位寄存器模块由FPGA芯片的LPM_SHIFT-REG(移位寄存器)兆功能实现。校验位验证模块用到了LPM_DIVIDE(除法)和LPM_COMPA RE(比较器)兆功能。

SOPC模块设计基于NiosⅡ软核嵌入式微处理器,利用FPGA 中的可编程逻辑资源和IP软核可以方便地构成嵌入式微处理器的接口功能模块,SOPC模块包括NiosⅡ处理器、Avalon交换式总线、片内外存储器以及外设模块等。根据需要,可对NiosⅡ嵌入式系统裁剪,进行自己定制。SOPCBuilder软件自动生成Avalon总线,用户可以将处理器、存储器和其他外设模块连接起来,形成一个完整的系统。在本部分电路设计中,用到了NiosⅡ嵌入式处理器的片内存储器和中断功能。

在接收模块设计中,应着重考虑如何找到34位串行编码的起始位,这也是保证接收模块可靠性的关键。由于两个相邻码位的时间间隔为一个码位周期,所以可以采用计数超时方法对移位脉冲进行串行编码起始位检测,寻找起始位。起始位检测模块主要由计数器构成。超时门限的设定原则上应大于一个码位周期,而小于两个码位周期。该模块的输入时钟来自分频模块的32 MHz高稳定晶振。分频后的输入时钟为16 MHz,即以串行编码传输速率20倍的频率进行超时计数检测。

具体电路实现还要考虑串行信号传输时产生的信号畸变等因素,上述门限设定原则应有所冗余。从接收到一个码位到设定的时间门限之间,如果没有接收到其他码位,则可认为即将到来的下一个码位就是一个34位编码的起始位,此时将串入并出移位寄存器做清零处理,每接收完一个34位串行编码都应重新找一次起始位。从可靠性考虑,设计了移位时钟脉冲完整性检测电路,这样,即使接收偶尔出现误码,也不会影响其他34位串行编码的接收。

2.2 34位串行编码的发送

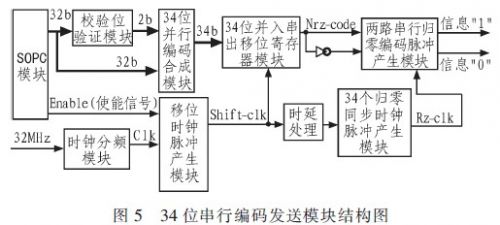

进行34位编码发送时,需要将所发送的32位并行数据转换为带有校验位的34位并行数据。SOPC模块将32位并行数据送入到校验位运箅模块,计算出两位校验位,32位并行数据与两位校验位送入34位并行编码合成模块,合并成34位并行编码。SOPC模块发出使能信号(Enable),使能移位时钟产生模块,该模块产乍移位时钟脉冲(Shift-clk),移位时钟脉冲经过时延电路后,产生归零同步时钟脉冲(Rz-clk)。

在移位时钟脉冲的作用下,34位并行数据在并入串出移位寄存器中逐位移出,形成两路极性相反的非归零串行编码(Nrz-code),与34个归零同步时钟脉冲相或后,即产生信息“1”和信息“0”的单檄性归零脉冲。单极性归零脉冲经电流驱动电路后,送入耦合变压器输出。在编码发送模块设计时,需要注意归零同步时钟脉冲与非归零串行编码的时序控制,防止出现“毛刺”信号,这可以采用触发器延时的方法实现。34位串行编码发送模块结构图如图5所示。

3 结束语

某专用接口装置采用34位串行编码与外部设备进行信息交换,该编码具有抗干扰性强,可靠性高的特点,适用于电磁环境恶劣情况下的信号传输。在该专用接口装置检测设备研制中,采用以FPGA芯片为核心的可编程逻辑设计以及SOPC软核设计技术实现了该类型编码的接收、发送电路。试验表明:设计的34位串行编码收发模块可靠性高,即使在文际测试信号有比较明显畸变的情况下,收发也未出现错误,功能完全满足要求,能够实现专用接口装置的接口功能检测。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码