FPGA设计开发软件Quartus II的使用技巧之: 约束及配置工程

5.7 约束及配置工程

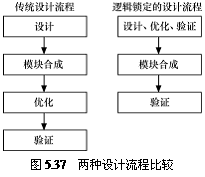

设计好工程文件后,首先要进行工程的约束。约束主要包括器件选择、管脚分配及时序约束等。时序约束属于较为高级的应用,通过时序约束可以使工程设计文件的综合更加优化。下面对这几种约束方式进行介绍。

5.7.1 器件选择

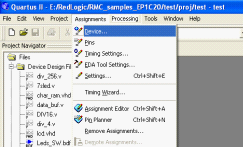

选择“Assignments”菜单中的“Device”选项,如图5.29所示。

图5.29 选择器件

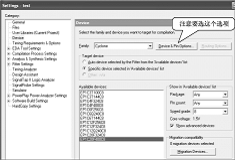

在打开的器件设置对话框中,选用cyclone系列ep1c12Q240c8(或ep1c6Q240c8)型号FPGA,速度等级为8,如图5.30所示。

图5.30 器件选择设置对话框

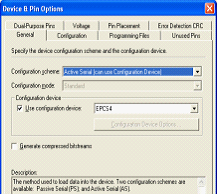

除了选择器件的型号外,还要注意要选择“Device Pin Options…”选项,打开器件配置对话框。在“General”选项卡中设置配置的方式(AS模式或JTAG模式),并选择配置器件,如EPCS4,如图5.31所示。

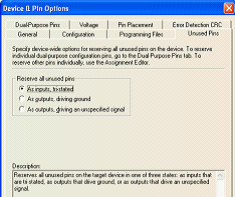

在“Unused Pins”选项卡中可以设置未使用管脚的工作状态,如设置成输入三态,如图5.32所示。

图5.31 设置配置模式 图5.32 未使用管脚设置

5.7.2 管脚分配

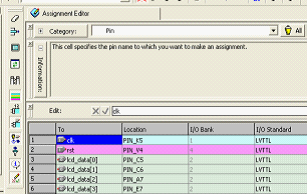

选择器件后,就可以为设计文件进行管脚分配了。选择“Assignments”菜单中的“Pins”选项,打开管脚分配器,如图5.33所示。

图5.33 管脚分配器

已经编译过的所有输入输出信号都会自动显示在分配列表中,无需手动添加。按照用户的设计需求进行管脚定义,然后再编译整个工程文件,即可进行下载。

5.7.3 时序约束

分配管脚后,在执行完全编译(Full Compilation)之前,可以利用“Assignments Editor”和“Settings”菜单的“Timing Requirements Options”对系统信号的时序特性进行设置,也可以使用“Timing wizard”向导来设置时序约束条件。

设置时需约束后,经过完全编译,Timing Analyzer即可对设计自动进行时序分析。也可以在完全编译期间进行时序分析,或在初始编译后单独进行时序分析。然后使用报告窗口、时序逼近布局图和list_path_tcl命令查看时序结果。

时序约束要求允许为整个工程、特定设计实体或个别实体、节点引脚等设置所需的速度性能。如果未指定时序约束条件,Timing Analyzer将使用默认设置运行分析。

一般的时序约束包括最大频率、建立时间、保持时间、时钟至输出延时、引脚至引脚延时以及最低时序要求等。还可以对多个时钟域、路径切割选项和默认外部延时等进行设置。下面是几种常见约束的定义。

· fmax(最大频率):在不违反内部建立时间(tsu)和保持时间(th)要求下可以达到的最大时钟频率。

· tsu(时钟建立时间):在触发寄存器计时的时钟信号已经在时钟引脚确立之前,经由数据输入或使能端输入而进入寄存器的数据必须在输入引脚处出现的时间长度。

· th(时钟保持时间):在触发寄存器时钟信号已经在时钟引脚确立之后,经由数据输入或使能端输入而进入寄存器的数据必须在输入引脚处保持的时间长度。

· tco(时钟至输出延时):时钟信号在触发寄存器的输入引脚上发生转换之后,再由寄存器馈送信号的输出引脚上取得的有效输出所需的时间。

· tpd(引脚至引脚延时):指定可接受的最少的引脚至引脚延时,引脚处信号通过组合逻辑进行传输并出现在外部输出引脚上所需的时间。

运行时序分析或者完整编译之后,在“Processing”菜单中选择“Compilation Report”选项,在弹出的报告栏中选择“Timing Analyzer”即可产看分析结果。

5.7.4 配置工程

下面来介绍最常用的两种FPGA配置模式。

1.JTAG模式

JTAG模式直接将逻辑下载至FPGA。这种模式下载速度快,但掉电即失,适合进行电路调试时使用,下载文件类型为sof文件。

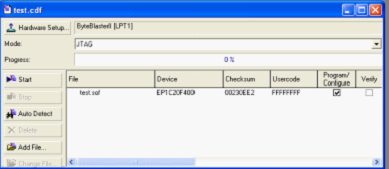

首先确认电缆已连接到主机与FPGA实验平台的JTAG插座上,选择“Tools”菜单的Programmer下载器,如图5.34所示。

图5.34 选择下载器

打开如图5.35所示的下载器后,通过“Hardware Setup”按钮选择下载电缆(如USB、LPT、ByteBlasterII等)。然后选择JTAG下载模式,并把“Program/Configure”勾上,即可进行下载。

图5.35 下载器对话框

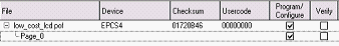

2.AS(Active Serial)模式

AS模式将逻辑下载至配置芯片上(如EPCS4)。这种模式下载速度相对较慢,但掉电不失,适合调试结束后固化最后版本逻辑时使用,下载文件类型为pof文件。

首先确认电缆已连接至AS插座上。选择“Tools”菜单的Programmer下载器,同样选择电缆后,选用AS下载方式,再将“Program/Configure”勾上,即可下载,如图5.36所示。

图5.36 AS下载模式

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码