全新EDK8.1简化嵌入式设计

在到达了一个行业里程碑之后,下一步是什么呢?2005年,包含在嵌入式开发套件(EDK|0">EDK)中的Xilinx® Platform Studio工具套件因其嵌入式设计创新而荣获IEC的DesignVision大奖。这个革命性的设计向导方法给原本依赖手工而且容易出错的嵌入式系统开发过程注入了抽象思维和自动化理念。

2006年,赛灵思公司(Xilinx)又针对Platform Studio工具套件发布了一个新的版本8.1,强调对开发过程的简化并且提供了一个更加直观的环境。该成果对于新手来说可以缩短学习时间,对于现有的设计者来说,则意味着一个更加完善和易于使用的环境。

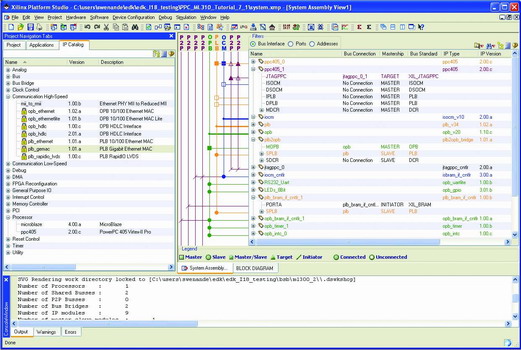

Xilinx对Platform Studio的主用户界面进行了升级,为软硬件工程师带来直观感受……

复杂设计的启动阶段往往就要占用大量时间,因此作为先行条件,Xilinx帮助客户完成核心设计的最初步骤是自动实现的。Platform Studio工具套件中的Xilinx基系统生成器(Base System Builder)设计向导可带你逐步完成设计中甚为关键的最初阶段。设计向导是一个伟大的创新,因为它们能够提供到达核心设计的快捷途径,即使你毫无经验。安装的向导越“聪明”,产生的问题越少,那么使用者所要求具备的经验也就越少。

预知配置的硬件/软件开发套件也非常有价值,它们可以使设计迅速脱离“婴儿期”,到达一个快速、稳定的阶段。Xilinx硬件/软件开发套件提供了硬件板、硬件识别工具和预先经过验证的参考设计。这样做的好处是,您可以在短时间内给硬件加电,将可用的设计方案下载到开发板,然后对核心系统进行研究,从而避免过去对新硬件、新固件和新软件一起进行调试所带来的延迟和复杂度。

在进行全系统验证以前,嵌入式设计的大部分时间都花在对核心设计进行迭代,逐步引入新特性,增加独立功能并且在每一步之后进行重复调试等方面。由于这些工作非常单调而且耗费时间,该阶段应尽可能的简单、有效。版本8.1着重于将普通(和重复性)任务变得简单和直观,从而让新用户和现有用户从中获益。

所有用户都将从V8.1中受益

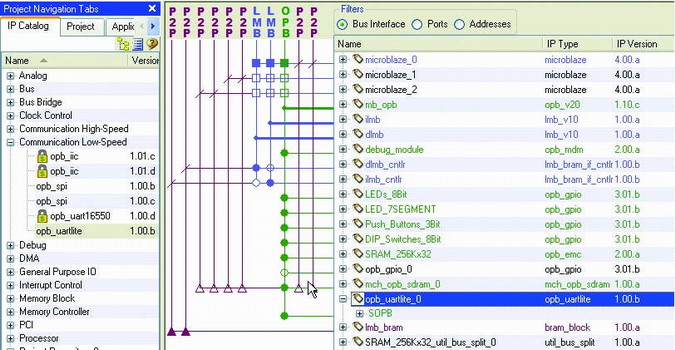

Xilinx对Platform Studio的主用户界面进行了升级,为硬件和软件工程师带来直观感受,这使得多视图和定制对于所有用户来说都变得更加容易。图1中的集成开发环境(IDE)显示了丰富的信息,但是也允许过滤视图和定制工具栏。左侧面板提供了标准的“tab(标签)”方法,用于在“Project”、“Applications”或者“IP Catalog”中显示或者隐藏信息面板。只需要切换标签就可以显示面板内容。

|

您可以在“Applications” 标签下观察软件应用,通过对标签所属内容的浏览,可以访问构成嵌入式系统设计的所有C语言源文件和头文件。该视图还可以对编译选项甚至Block RAM初始化过程进行观察。

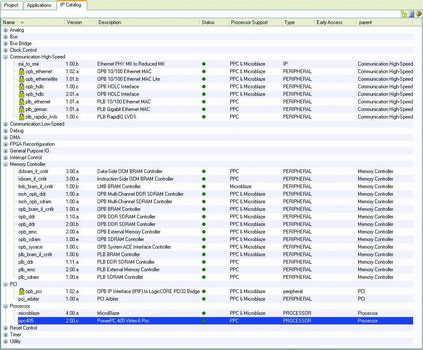

“IP Catalog” 标签中包含有与设计相关的IP核的建立、购买或引入的详细信息。对于时间有限的评估而言,Xilinx为嵌入式开发套件软件包中的处理IP核以及某些高价值IP核提供了多种评估方式。如需了解Xilinx处理器IP方面的更多信息,请登录网站:www.xilinx.com/cn/ise/embedded/edk_ip.htm。

中间面板是“Connectivity”互连关系视图,右侧的相邻面板是与之相关的“System Assembly”视图。Connectivity互连关系视图对设计的总线结构进行了直观显示,并且提供了一个动态工具用于创建或者编辑现有连接。着色编码视图可以使总线类型和它与IP之间的关联方式变得一目了然(甚至对于刚入门的用户也是如此)。举例来说,在这个视图中,和PLB|0">PLB(处理器本地总线)相连的外设被标成桔红色;OPB|0">OPB(片上外设总线)的连接标成绿色;和处理器核(这里是PowerPC 405)进行的点对点连接被标成紫色。面板上的“filter”按钮允许您对连接视图进行定制或者简化,从而使您可以更加专注于特定的总线元件,而不受其它元件的干扰。

Platform Studio通过装配来保持正确的连接,从而减少设计人员可能发生的错误——也就是说,XPS将仅显示彼此兼容的总线类型的连接选项。这避免了使用支持不兼容连接的工具所带来的调试痛苦。

|

但是,如果您的项目和设计团队需要设计的文档资料,Platform Studio 8.1也具有强大的功能,它可以生成全面的设计参考材料,包括系统元件和它们之间互连的完整框图。文档的自动生成节约了宝贵的时间(否则需要手动建立这些资料),同时减少了文档资料的出错率。这种方法将文档和设计保持精确同步,还能够显示整个项目的清晰视图。

新的增强功能使现有用户受益

|

该工具还可提供额外信息,比如IP支持哪种类型的处理器。因为Xilinx支持高性能PowerPC硬核和灵活的MicroBlaze™软处理器核,所以了解处理器的专用IP核很有好处。实际上,在右击catalog中的一个IP核,就可以快速访问IP核的修订历史以及相关细节的完整PDF说明书。为了清晰起见,外设的驱动程序也有一个类似的平台设置视图,包括版本控制以及嵌入式OS支持。

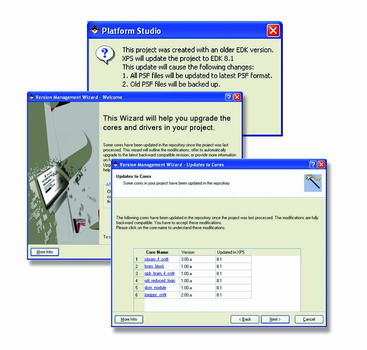

当新版本工具和IP核可用时,设计的向上移植就应变得尽可能简单。没有人愿意重新投入设计、调试以及接受时间的检验,然后才将一个旧设计移植到新工具或者IP核上去。新IP核/工具具有很大的升级优势。Platform Studio 8.1具有移植能力(图4),使您可以通过向导,快速、自动地完成移植。

|

致力于复杂代码应用的软件开发人员,会很高兴看到基于Eclipse的XPS软件开发套件IDE的性能得以增强。XPS-SDK具有一个升级的工具栏,它既可以对相似功能和按钮进行更加逻辑化的分组,同时又允许进行用户定制。版本8.1引入了一个更加强大的C/C++编辑器,它支持函数、方法、类、结构和宏的代码折叠功能,还对编译器进行了改进。这些新的支持功能可以指定(目标代码)连接器脚本,并且能够为PowerPC、MicroBlaze处理器核和C++类创建向导定制编译器选项。将这个强大的软件环境和创新的性能视图以及集成式硬件/软件调试器独一无二的XPS功能结合在一起,8.1的用户将会在更少的时间内创造出比以前更好、更强大的嵌入式系统。

总结

屡获大奖的Platform Studio使嵌入式系统设计变得更为简单流畅。自动设计向导和预知配置的硬件/软件开发套件有助于快速启动设计,同时可以减少错误和追尾现象。

既然我们在加速“入门”过程方面的成功获得了业界认可,那么,现在就该对处于开发过程核心的耗时问题和循环问题进行改进。创建——调试——编辑——重复。您是否用过大部分步骤都是直观的计算机辅助工具呢?在没有阅读内容明晰的手册或者电脑界面之前,您何从知道每一个按钮的作用呢?

EDK/XPS版本8.1专注于改进整个开发板的易用性,包括对主用户界面、软件开发环境(包括编辑和编译)、IP升级、旧项目移植、设计记录、总线系统查看和编辑以及其他内容的改进。

通过使普通任务变得更简单和直观,不管是对经验丰富的嵌入式工程师,还是对于刚刚接触可编程FPGA|0">FPGA平台(并且含有处理器)设计方案的新手来说,我们都可以使设计过程变得更加轻松。利用开发过程中节省下来的时间来革新自己的嵌入式产品吧。

如需了解8. 1版EDK和所有嵌入式处理解决方案方面的更多信息,敬请登录网站:www.xilinx.com/cn/edk。

作者:Jay Gould 赛灵思公司(Xilinx Inc.) Xilinx嵌入式解决方案市场部产品营销经理 @xilinx.com">jay.gould@xilinx.com

关键词: Xilinx PlatformStudio EDK IDE PowerPC FPGA OPB PLB MicroBlaze

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码