100MHz 数字存储示波表样机的研究与试制----数据采集系统设计(四)

3.4.4峰值采样

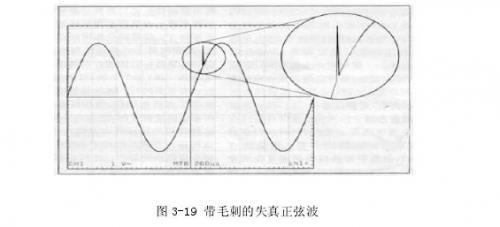

峰值采样是数字存储示波器的重要技术之一,它主要用来捕捉信号波形的毛刺以及实现波形的包络显示。如果我们使用模拟示波器来观察如图3-19所示的失真正弦波,那么只有当毛刺是重复性并且与主信号同步时,我们才有可能看到这个毛刺。但由于毛刺常常是源于其他的电路系统,所以这些毛刺信号往往是随机而且与主信号不同步的。

数字存储示波器要想准确的捕捉到毛刺,其中一个有效的方法就是提高采样率,减少采样点之间的时间间隔,使得采样点能够落在随机出现的毛刺上。但一味追求高采样率随之而来的问题就是存储空间的不够用,从而导致捕获时间的减少。例如,峰值采样的典型应用是观察某些电路故障的长时间记录,从中寻找毛刺或其他不规则现象。如果我们只有5K的存储深度,当采样率为50MHz时可以进行的最长捕获时间为100μS,而当采样率提高到1GHz时,最长捕获时间则缩短为5μS.所以,提高采样率与有限的存储深度之间存在着矛盾。解决这一矛盾的方法就是峰值采样。

采用峰值采样时,示波器始终以最高的采样率采样,在每个取样间隔中捕获信号波形的最大和最小值,并由正负峰值检测器将信号的最大、最小值暂时存储起来。当示波器要显示采样点的时候,示波器就用捕获的信号的最大最小值来代替原来的采样点数值,并将该峰值检测器清零。因此,峰值采样能够帮助我们发现由于取样间隔过宽而丢失的毛刺信号。

示波器上的峰值检测分为硬件(模拟)峰值检测器和数字式峰值检测器。模拟峰值检测器是一个专门的硬件电路,它以电容上电压的形式存储信号的峰值。这种的缺点是速度比较慢,它通常只能存储宽度大于几个微秒且具有相当幅度的毛刺。数字式峰值检测器是围绕AD而构成的,这时AD将以可能的最高采样速率连续的对信号进行采样,然后将峰值存储在一个专用的存储器中,当要显示采样点的时候,存储的峰值就作为该时刻的采样值来使用。数字式峰值检测器的优点是其速度和数字化过程的速度一样快。

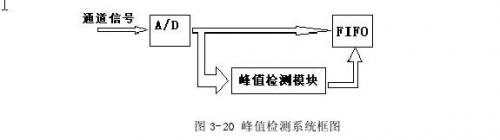

本项目中,我们采用了数字式峰值检测方式。系统框图如图3-20.

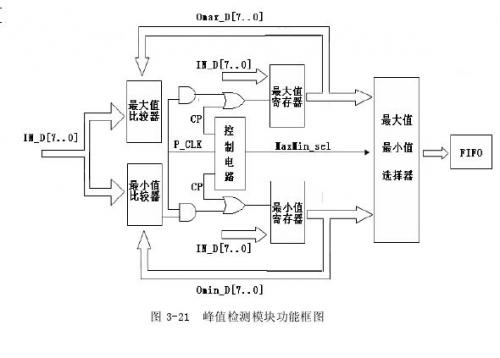

在实际电路设计中,由于受FPGA速度的影响,AD的采样率不能设置为最高的100MHz,而是采用固定的10MHz.如图所示,调理通道出来的模拟信号经A/D采样后并不像普通采样那样直接进入FIFO,而是先经过峰值检测模块筛选出最大最小值后,再将最大最小值存入FIFO.写FIFO的时钟由时基档位决定。这样将AD采样时钟和写FIFO时钟区分开来,使得在低时基档位下同样能够捕捉到信号的毛刺。峰值检测模块的功能框图如图3-21.

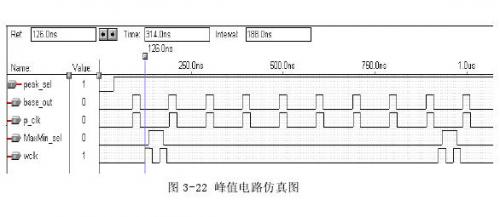

由图可知,整个峰值检测模块主要由两个比较器,两个寄存器,最大最小值选择器以及控制电路组成。从AD送来的数据首先进入最大最小值寄存器,作为比较的初值,再与后面送进来的数据相比较。比较过程中的最大最小值再分别存入最大最小值寄存器。比较完一组数据后,控制电路连续发出两个FIFO写脉冲,将这组存储在最大最小值寄存器里的数据写入FIFO.当写FIFO结束以后,控制电路紧接着再发出一个CP脉冲,将下一组的第一个数据写入最大最小值寄存器,作为第二组比较的初值。峰值检测电路的时序仿真如图3-22.

其中的peak_sel信号为峰值功能选择信号,当peak_sel为高电平时,峰值功能被选中。base_out和p_clk分别为采样脉冲和比较脉冲,它们同为10MHz.即从AD进来一个数据就马上进行比较,比较结果作为最大最小值寄存器的锁存信号。从图3-19可以看到,AD数据同时送入比较器和寄存器,这就保证了当比较结果为真时,数据就会立即被写入寄存器。wclk信号为FIFO写时钟,它的电路要求是必须在前一组最后一个数据采进来之后,后一组第一个数据采进来之前,完成两次写FIFO的操作。MaxMin_sel信号为最大最小值选择信号,当它为低电平时,最大值写入FIFO;当它为高电平时,最小值写入FIFO.

由于峰值检测是以一组采样点中最大最小值的形式存储一个事件的幅值数据,所以事件的定时分辨率是无法知道的,它只能以峰值检测间隔的分辨率来显示检测到的事件。例如,示波器的AD以1GSPS(1ns间隔)采样,而峰值检测的采速为10MSPS(100ns间隔),快速事件将以100ns分辨率进行显示,而不是以AD采样的1ns.从AD来说,100ns之间有100个采样点,如果100个采样点中不止一个快速事件,而示波器也只能捕捉到这些事件中的最大值和最小值。

3.5 SCAN方式下的数据采集

当示波器的时基档打到某一档位的时候,示波器开始使用SCAN方式(即扫描方式)来显示波形。扫描方式主要用来观测低频信号和变化缓慢的信号。工作在扫描方式下的示波器就像一台图像记录仪,记录笔在屏幕右端,纸由左向右移动。当扫完一屏后,在显示新波形的同时删除旧波形数据,新波形与旧波形之间有一格的空白区来加以区分。由于扫描方式主要是用来观测低频信号和变化缓慢的信号,所以如果采用通常的触发方式来显示波形的话,触发条件会很难满足,故示波器工作在扫描方式下时不考虑触发信号。

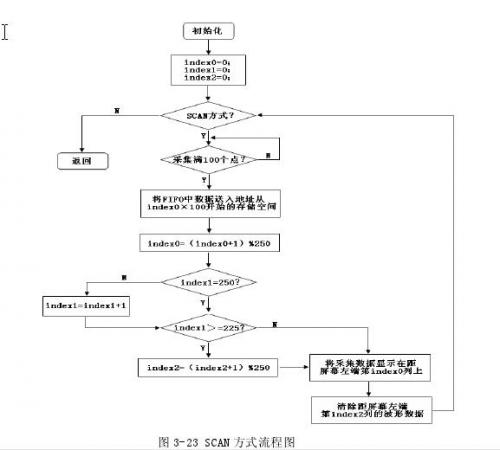

本项目中,我们设计当时基档打在100ms/div和更高的档位时采用扫描方式。具体的实现流程如图3-23.

从图中我们可以看到扫描功能主要由index0,index1,index2三个计数器来完成。其中,index0中的计数值表示最新显示数据距显示屏左端的距离,它的范围为0~249;index1中的计数值表示波形没扫完一屏时距显示屏左端的距离,范围为1~250;index2中的计数值表示要清除的旧波形距显示屏左端的距离,范围为0~249.它的具体实现过程是:首先初始化,将index0,index1,index2设置为0,然后判断是否设置为扫描模式。当确认为扫描模式后,判断FIFO里是否采集够100个点。采满100个点后,将这100个数据存入相应的存储空间,并使index0,index1开始计数。当index1计数到225的时候,也就是新波形数据已经扫描完第九格时,index2开始计数,即开始清除显示屏最左端第一列的最老数据,这样保证了新波形与旧波形之间有一格的空白显示区。当扫描完一屏后,即index1计数到250的时,其值不再变化,保持250不变。注意,在扫描模式下不考虑触发信号,AD不停的采样,一次性写入FIFO 100个点。显示时读出这100个点,从中选出最大值和最小值,再与前面最近的点比较,选出最终的最大最小值,显示在同一坐标轴上。每显示和清除一列波形,屏幕刷新一次。

3.6时基电路的实现

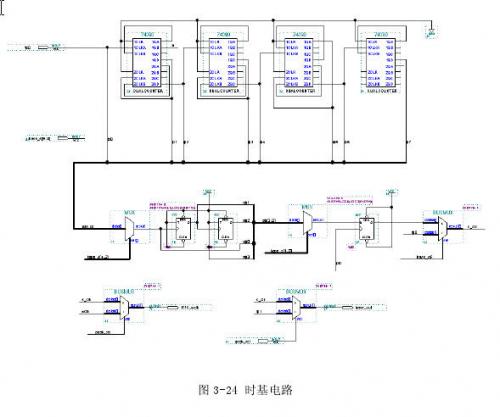

时基电路是数字存储示波器的重要组成部分,它的作用主要是提供AD的采样时钟和FIFO的写时钟。它的电路实现如图3-24.

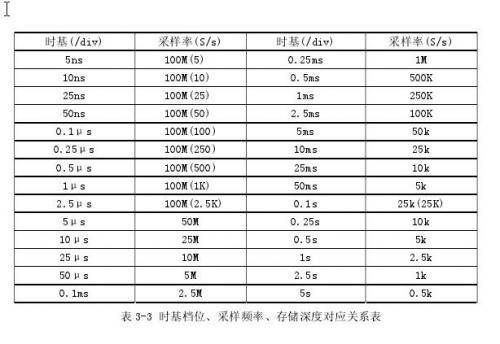

图中fp0为源时钟,它是由外部晶振提供的标准100MHz频率信号。进来的100MHz频率信号经过由四个74390和两个T触发器构成的二分频、四分频器组成的分频网络,按照1、2、5步进的方法产生所需要的AD采样频率和FIFO写时钟。在示波表的控制面板上有一个时基控制按钮sec/div,不同的时基档位下对应着不同的采样频率。每选择不同的时基档位时,图中的base_sel[5..0]信号即时钟选择信号就会输出不同的值以选择与档位相应的采样时钟。具体的时基档位与采样时钟以及每个档位下存储深度的对应关系如表3-3.另外,从图中我们还可以看到有两个由peak_sel作为选择信号的选择电路。这主要是用来实现在峰值检测时特殊的写FIFO时钟和固定AD采样频率为10MHz.(请参考3.4.4节)

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码