基于ADF4106的低相噪本振设计

编者按:为了实现低相噪的本振信号输出,本文设计出一种基于锁相环芯片ADF4106的低相噪本振源。通过实际调试,测试结果满足设计要求,并作为第二点频本振应用于一款通信测试仪器的中。

作者/ 曹阳1 ,2 1.中国电子科技集团公司第41研究所 研发1部(安徽 蚌埠 233006) 2.电子信息测试技术安徽省重点实验室(安徽 蚌埠 233006)

*基金项目:国家科技重大专项面向R12 LTE-Advanced终端综合测试仪(编号:2016ZX03002010)

曹阳(1989-),男,助理工程师,研究方向:通信测量仪器的研究与开发。

摘要:为了实现低相噪的本振信号输出,本文设计出一种基于锁相环芯片ADF4106的低相噪本振源。通过实际调试,测试结果满足设计要求,并作为第二点频本振应用于一款通信测试仪器的中。

引言

低相噪本振是通信测试仪器等现代电子设备系统的核心模块,它对电子设备系统的性能起着决定性的作用。对于低相噪本振的设计,许多人做了大量的研究[1-4],本文利用锁相环芯片ADF4106设计出一种低相噪本振源,作为第二点频本振应用于一款通信测试仪器中,为测试仪器提供一个5400MHz的下变频信号。

1 方案设计

1.1 设计指标

输出频率:5400MHz

相位噪声:≤-110dBc@1kHz

相位噪声:≤-118dBc@10kHz

输出功率范围:10~12dBm

1.2 设计方案

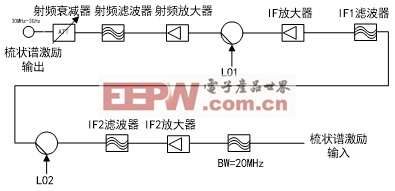

本方案利用Z-COM公司的压控振荡器CRO5400Z产生5400MHz的输出频率,经过功率分配后,一路通过功率调理电路后输出给整机作为第二点频本振,另一路反馈进入具有分频、鉴相功能的ADI公司的可编程锁相环芯片ADF4106,与100MHz参考经过分频后进行鉴相,通过环路滤波器滤波后驱动压控振荡器产生5400MHz的输出频率。原理框图如图1所示。

2 关键电路设计

2.1 ADF4106电路设计

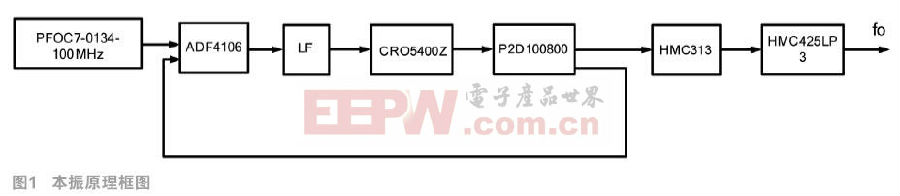

ADF4106由一个数字鉴相器PD、一个充电泵CP、一个可编程的基准分频器、可编程的A(6位)、B(13位)计数器及一个双模式的前置分频器(P/P+1)组成。内部结构原理图如图2所示。

利用ADF4106和环路滤波器LF(Loop Filter)、压控振荡器VCO(Voltage Controlled Oscillator)可以构成一个锁相环PLL(Phase Locked Loop)。根据ADF4106datasheet提供的公式:

![]()

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码