Zynq-7000的柔性直流输电桥臂控制器设计

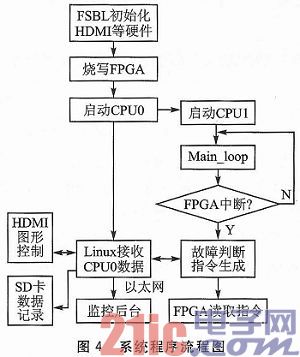

Linux内核在CPU0启动成功后,此时CPU1处于休眠状态,会一直轮询0xFFFF FFF0地址处的数值,非零就把读取到的数值装载到PC寄存器,跳转到对应的地址执行指令。CPU0通过Linux的devmem命令把CPU1的DDR3内存起始地址0x3000 0000写入0xFFFF FFF0,启动CPU1:devmem 0xFFFF FFF0 0x3000 0000。

CPU1启动后,在主函数注册中断服务函数,当FPGA的数据中断发生时进入中断函数,进行故障判断并生成控制指令。因为CPU1运行的是裸机程序,其中断响应时间要比运行Linux的CPU0响应时间短。

3. 3 系统软件升级

桥臂控制器在调试过程中经常需要对代码进行升级,而程序代码和FPGA的配置文件固化在外部Quad-SPIFlash中,通过开启CPU0上Linux的SSH和FTP服务,使用网口可以重新烧写Flash中的文件,步骤如下:

①PC电脑通过FileZilla Client(Windows下的ftp工具)登录Linux的ftp服务器,将新的烧写文件上传到Linux的文件系统下;

②PC电脑通过putty(Windows下的ssh工具)登录Linux的root账号;

③在putty界面下,使用Linux自带的flashcp命令将上传的文件烧写到外部Quad—SPI Flash。

桥臂控制器重启后,系统软件得到更新。

3.4 应用程序流程

系统程序流程如图4所示。

4 FPGA通信传输率测试

ARM和FPGA通过AXI4数据总线进行通信,数据带宽最高达到1 024位,本文主要测试了64位突发传输率。

对于64位突发传输,分别测试FPGA工作频率为50 MHz、100 MHz和150 MHz时,FPGA发送256个64位数据的用时,如表1所列。

由表1可以计算得出不同FPGA工作频率下,数据位宽为64位时的传输速率,如表2所列。

由表2可见,使用zynq—xc7z020芯片能够极大提高FPGA和ARM的数据传输速率。

结语

本文设计的桥臂控制器,采用Xilinx Zynq—xc7z020芯片,使用AXI总线取代了以前的DSP+FPGA数据总线方式,实测的最高数据传输率达到8.9 Gb/s,极大地改善了阀控系统数据通信的实时性,同时简化了控制板卡的硬件设计,降低了板卡功耗,提升了系统的运行稳定性。

利用芯片上集成的ARM Cortex-A9 MPCore双核处理器,搭建了AMP多系统架构,在保证系统实时响应FPGA中断的同时,移植了Linux操作系统,提供了人机交互界面,为桥臂控制器添加了新的控制功能,简化了柔性直流输电阀控系统的整体设计。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码