三相SPWM波形发生器的设计与仿真

编者按:本文提出了一种采用VHDL硬件描述语言设计新型三相正弦脉宽调制(SPWM)波形发生器的方法。该方法以直接数字频率合成技术(DDS)为核心产生三相SPWM信号。并且利用VHDL设计了死区时间可调的死区时间控制器,解决了传统的模块电路等待方法很难产生带精确死区时间控制的SPWM信号的问题。该方法在Quartus II 9.1环境平台下进行了仿真验证,并将设计程序下载到DE2-70实验板进行实验测试,用示波器测试得到了死区时间可控制的SPWM波形。

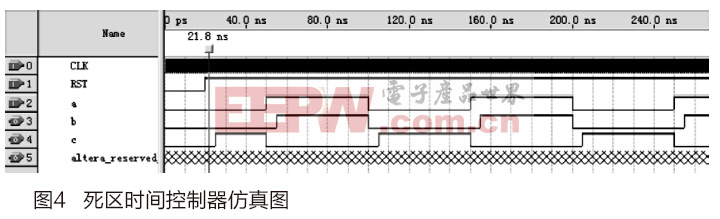

摘要:本文提出了一种采用VHDL硬件描述语言设计新型三相正弦脉宽调制(SPWM)波形发生器的方法。该方法以直接数字频率合成技术(DDS)为核心产生三相SPWM信号。并且利用VHDL设计了死区时间可调的死区时间控制器,解决了传统的模块电路等待方法很难产生带精确死区时间控制的SPWM信号的问题。该方法在Quartus II 9.1环境平台下进行了仿真验证,并将设计程序下载到DE2-70实验板进行实验测试,用示波器测试得到了死区时间可控制的SPWM波形。

引言

三相正弦脉宽调制(SPWM)技术在三相逆变电源系统、交流电机调速系统等领域有着广泛的应用[1] ,并且发挥着核心的作用。SPWM发生器是应用系统设计中的一个难点,目前SPWM波形发生器的设计方法有以下几种:(1)采用模拟电路的方法,用分立元件构成三角波、正弦波信号发生器,再通过LM311等比较器进行自然采样后输出SPWM波形。该方法对元件参数稳定性和电路可靠性要求过高,且输出信号的精度不高。(2)采用专门的SPWM波形发生器集成电路芯片,如SLE4520、SA4828等[2],但这些专用芯片的功能单一,使用不灵活。(3)随着数字芯片的发展,复杂可编程逻辑器件(CPLD)、现场可编程门阵列(FPGA)等器件得到广泛的应用。因此设计基于CPLD/FPGA器件的波形发生器是目前流行的方法[3] 。在SPWM信号发生器的设计中,产生死区时间可任意调节的SPWM信号一直是一个难点。本文利用VHDL语言设计了死区时间控制器,使得输出的两路SPWM信号的死区时间可以任意调节。本文在Quartus II 9.1平台下,采用VHDL语言与DDS技术相结合设计了一种带死区时间控制器的三相SPWM波形发生器,并在DE2-70实验平台下进行了验证。

1 方案设计

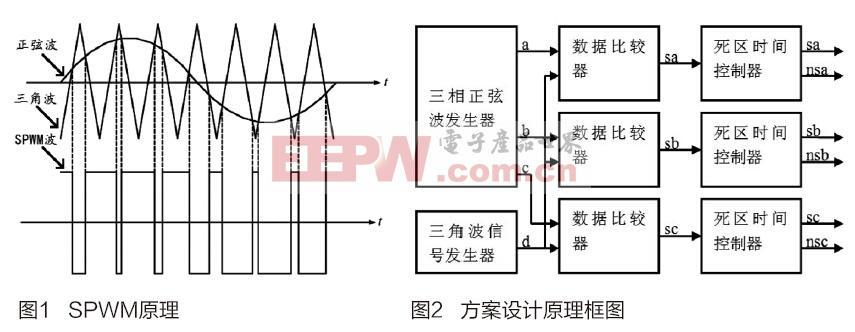

采用三角波为载波,对正弦波进行自然采样比较的方法输出SPWM,其采样的原理如图1所示。

本文设计思想为在FPGA/CPLD内存中分别存储了离散的三角波数据、正弦波数据,再利用DDS技术输出三角波数据和正弦波数据,设计一个数据比较器对以上两种波形数据进行实时比较,如果正弦波数据大于三角波数据,SPWM信号输出高电平,反之则输出低电平。根据以上原理,利用DDS技术产生相位差为120o的三相正弦信号分别与三角波信号进行比较,就能输出三相SPWM波形。

系统的总体框图如图2所示。信号a、b、c为三相正弦波数据,分别与信号d三角波数据进行比较后输出sa、sb、sc为三相SPWM波,再经过死区时间控制器后,最终得到6路SPWM波形输出。其中sa与nsa波形为反向,sb与nsb波形为反向,sc与nsc波形为反向。

2 三相正弦波发生器模块

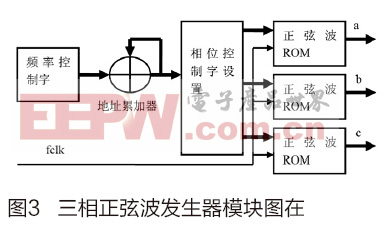

三相正弦波发生模块如图3所示,该模块根据传统的DDS模块框图进行优化与改进。其原理是由时钟信号fclk控制累加器模块按顺序生成ROM的地址,将存储在ROM中的正弦波形数据逐个输出。

本设计中地址累加器模块地址宽度N为二进制16位,该累加器主要完成频率控制字的累加功能,从而得到ROM的寻址地址;正弦波ROM的数字位宽为8位,存储深度为256;相位控制器设置模块主要完成设置三个正弦波a、b、c的初相位差为120o的功能。由于正弦波ROM的地址线宽度为8位,而地址累加器地址宽度为16位,所以本文取地址累加器的高8位与正弦波ROM的地址线相连接。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码