X波段频率合成器设计

3 电路设计

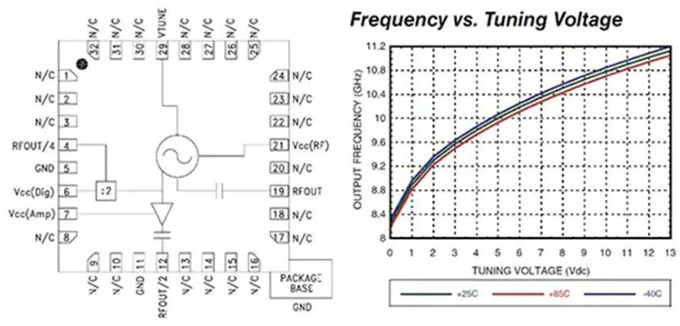

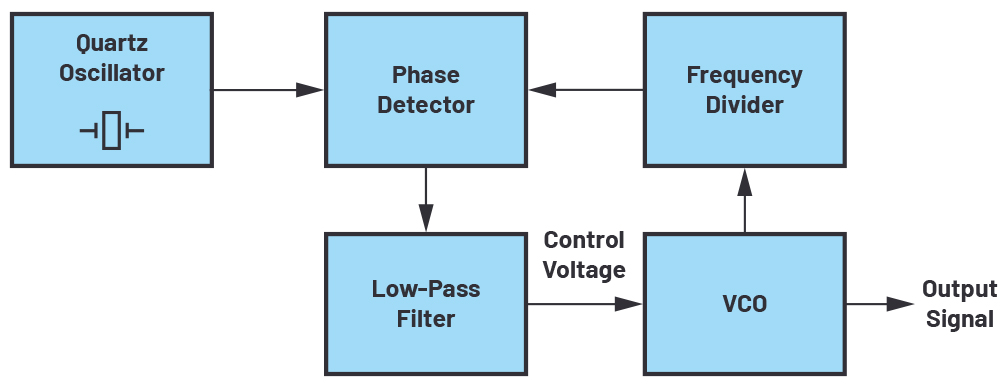

X波段频率源的设计重点在于选择合理的PLL输出、锁相环路滤波器的设计以及电路PCB布板和电磁兼容设计。

3.1 环路滤波器的设计

环路滤波器是锁相环电路中最重要的一个部分,它的性能好坏直接关系到锁相输出的相位噪声和杂散指标,锁定时间。环路对带内噪声呈低通滤波,对VCO噪声呈高通特性,所以选择环路带宽在两噪声源谱密度的交叉点附近总是比较接近于最佳状态的。环路滤波器分为有源滤波和无源滤波,当VCO的调谐电压超过鉴相器的最大输出电压时,就要用到有源环路。使用有源环路时,选择合适的运算放大器对环路的性能有很重要的影响,主要影响的参数有噪声电压、噪声电流、转换速率、偏置电流。其中噪声电压、噪声电流主要影响输出信号的相噪特性,而转换速率、偏置电流对杂散和转换时间的影响较大。此外运算放大器的偏置电压对输出信号的相位噪声影响也较大。

3.2 PCB的布板和电磁兼容设计

3.2.1 优质电源和良好的电源滤波

对于PLL电路,要得到频谱纯度高的信号,电源稳定度是非常主要的指标。可选用串联稳压器,做好直流电源与控制电源的去耦来减小外界信号对电源的干扰。

3.2.2 合理的布板

鉴相器中充电泵的供电线最易受到噪声信号的影响,可在Vcc和充电泵的供电线上放置去藕电容。容值为0.1mF, 1mF和10mF的电容能在宽频率范围内滤出噪声。一般把较小的电容靠近PLL芯片放置用来处理高频噪声,大些的电容放远些,最好在它们之间加电感。设计时确保充电泵供电线和VCO的调谐线路远离噪声源,尽量避免在VCO调谐线路的近端排布任何信号走线,调谐电压非常微小的变化也会使一个高增益VCO产生很大的频率偏移。对VCO应采用适当的屏蔽措施,任何具有靠近VCO谐振点频率的噪声都会很容易地被耦合至VCO并对其进行调制,当输出信号的谐波能量被耦合至VCO振荡回路中时就会产生寄生输出,影响输出性能。

4 实验结果

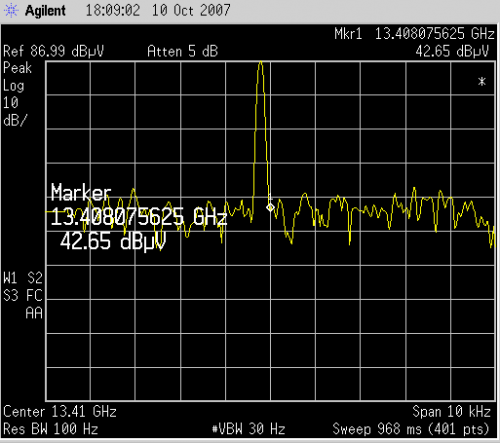

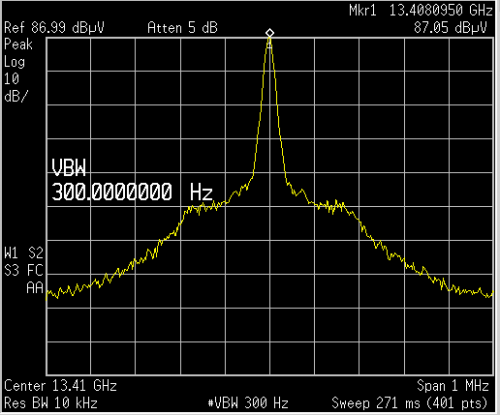

基于上面的理论和分析,我们研制出了输出频率为13.2~13.5GHz的频综系统,通过改变频率控制字和跳频步进,能够实现点频和以1MHz为步进的跳频输出。图2为PLL输出频点为13.41GHz时的相位噪声, 图3为PLL输出频率为13.41GHz时宽带杂散谱,鉴相频率为1MHz。由图可见,PLL输出的相位噪声达到指标所给的-65dBc/Hz@1kHz, 输出杂散也得到很好的抑制,对鉴相频率的抑制优于-80 dBc,输出杂散也得到很好的抑制。由于本实验受频率合成芯片中鉴相器噪声基底和分频器分频次数不连续的影响使得最终输出的相位噪声受鉴相器限制,故在实际应用中采用鉴相器噪声基底更低和分频次数连续的鉴相器相位噪声和杂散还可以得到一定程度的改善。

图2 相位噪声测试结果

图3 杂散测试结果

5 总结

通过对X波段微波频率合成器的设计和实验工作可以看到,采用PLL 频率合成方案构成的频率合成器的指标是令人满意的。从前面的分析和实验结果可知,PLL频率合成器在相位噪声特性、杂波抑制及频率分辨率等方面相对于单一的频率合成方式都较大的优势,其更大的优点还在于相对于多环锁相和混频锁相其结构简单、调试方便、性能稳定。因此PLL频率合成方案是用于频率合成器设计的一种较好的方案,可以推广至不同的频段和不同的应用。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码