X波段间接式频率综合器的设计

(2)杂散特性分析

实践证明,2:l的阻带/通带比是一个合理而实际的下限值。在这一原则指导下,我们可以根据中心频率f0附近杂散分布情况,合理选择带通滤波器的带宽和抑制指标。

240、300、1200MHz带通滤波器选用LC滤波器,其特性为在通带内插损较小(约3dB),而对于带外抑制应有70dB以上;低通滤波器也采用LC滤波器,其特性为在通带内插损较小(约1dB),而对二次谐波的抑制应达到40dB,这样15MHz和240MHz等信号的谐波、杂波抑制均可达到要求。

在锁相环内,由于环路自身的窄带跟踪滤波特性,可以使杂散减小至要求的范围内。实践证明,通过环路滤波器的优化设计以及采用良好的屏蔽措施,可使二本振的杂波抑制有很大的改善,可以达到-75dBc。

对一本振和主振合成源来讲,最关键的问题是要采取良好的隔离和滤波措施。通过提高功分器的隔离度,以及腔体分隔、减少共用部分,在很大程度上避免混频器LO端口的信号反串,使一本振和主振信号的隔离度达到要求;在三个混频器后面的滤波环节中,为抑制杂散,关键是滤波器的设计:我们采用了三个腔体微波滤波器,可以在保证220MHz通带内(对点频为窄带)插损较小(约2dB)的前提下,有效地滤除本振泄漏以及三阶交调等杂散分量,使一本振和主振信号的杂波抑制能满足要求。

(3)其它性能分析

对于0-π调相器,考虑到主振信号的BPSK调制精度为±3º,我们选用的调制器的插损≤3.2dB,幅度不平衡≤0.2dB,相位不平衡≤±2º,可以满足要求。

由于SPST1和BPSK的驱动电路延迟以及各自的响应时间不可能做到完全一致,它们的调幅码和调相码的时序需要通过主机进行适当的同步(响应快的要延迟一点)。

3 电路设计

3.1 PLL输出频段的选择(混频比设计)

在频综器的设计中,混频器的设计非常重要,一般应选择高隔离度高三阶交调的混频器。在选择好的混频器的基础上,混频比的设计变得更为重要,因为混频器会产生大量的交互调产物[1]。所以正确选择工作频率使交互调频率远离有用频率,以便滤波器较容易的滤除交互调频率,减小杂散输出。考虑到滤波器的性能的限制,我们选定LO2工作于L波段,使混频比为fLO2/fPDRO=0.1,同时适当减小输入幅度,可以降低高阶交调产生的杂散。

3.2 环路滤波器的设计

这里,选用较高的鉴相频率,可以加强锁相环抑制参考边带的能力。同时,较高的鉴相频率可以允许宽的环路带宽,从而加快频率捷变时间,保证跳频时间指标要求。

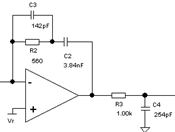

我们使用ADIsimPLL Ver 3.0来计算环路参数,如取fVCO=900~1200MHz,KV=30MHz/V,fn=200kHz,相位裕量为45°,可算得图2中的环路参数:

图2 PLL环路滤波器

在调试过程中,我们发现运放的噪声电压、噪声电流、转换速率、偏置电压/电流等参数对环路的相噪以及跳频时间影响特别大,所以必须采用优质的运放和电源。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码