一种基于FPGA的SOC设计方案

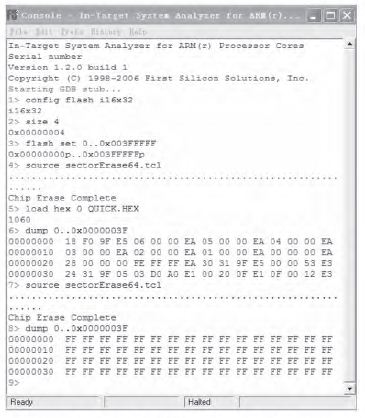

在图4中显示的是FS2工具的用户界面,设计中用到的八条指令,分别是:1>、2>、3>……8>,其中指令1>、2>用来配置片外Flash芯片;指令3>用来选择将要擦写的存储空间,由图中可知,本设计中要进行的读写操作 的存储空间是Ox00000000-0x003FFFFF;指令4>用来对Flash指定的存储空间进行擦除操作;指令5>用来把已经准备好的二进制文件写到上述存储空间中,设计中使用的二进制文件名是QUICK.HEX;指令6>是用来显示指定存储空间中的内容,从图中可看出,写到存储空间Ox00000000-0x0000003F的内容是18、FO、9F……、12、E3;指令7>执行对上述存储空间写入的数据的擦除操作;指令8>显示上述存储单元擦除后的内容。

图4 片外Flash的擦写演示过程

通过对上述过程的分析可知,所搭建的SOC系统可准确实现片外Flash的擦写操作,进而说明了该系统的准确性。

3.2 搭建的系统对外设接口的读写操作

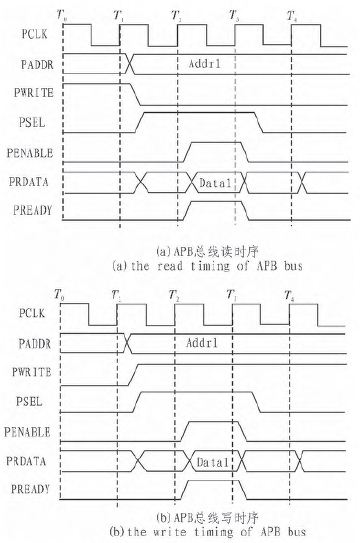

本测试在遵循ARM7先进外围总线APB的读写时序的前提下,定制用户逻辑外设PIO,通过该系统对PIO接口进行读写操作来进一步验证设计的准确,验证中的用到的APB总线的读写时序如图5。

图5 APB总线的读写时序

下面将主要遵循系统中先进的外围总线APB的读写时序,首先采用硬件描述语言和C代码,定制八位的用户逻辑外设PIO,然后将PIO的输入端口接到开关Switch0一Switch7,输出端口接到八个发光二极管Led0一Led7,通过软硬件调试,使八位开关的输入电平显示到八个发光二极管上,以此来进一步验证设计中搭建的SOC系统的准确,针对上述过程及要求,为了更直观地展示验证结果,制作了简单的实验板,当开关键在高电平时,发光二极管变亮,否则,发光二极管不亮。其中定制用户逻辑外设的主要步骤如下:

1)规划元件的硬件功能;

2)使用硬件描述来描述硬件逻辑;

3)单独验证元件的硬件功能;

4)描述寄存器的C头文件来为软件定义硬件寄存器映像;

5)将元件集成到ARM7系统中,使用ARM7来测试寄存器的访问是否正确,并为该元件编写软件驱动;

6)执行系统级的验证等。

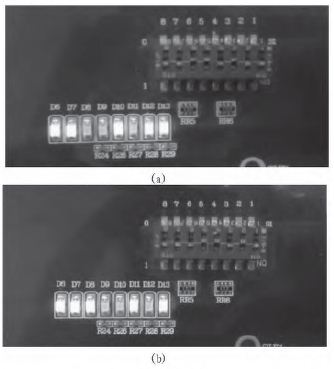

图6是在Aetel公司的调试软件Sofleonsole和实验板上的实际调试结果。

图6 调试结果

由图6显示的调试结果可知,八位开关Switeh0-Switeh7的输入分别是11001011和11100101,这个和八个发光二极管Led0-Led7的输出结果一致,由此进一步验证了设计的准确性。

4 结束语

本文通过对基于ARM7的SOC系统的设计,介绍了一种Flash结构的FPGA器件及其片上系统的设计方法,进而给出了两种验证该片上系统准确性的方法,通过实际验证,该系统不仅能准确进行片外存储器的擦写,而且可以准确进行外设接口的读写的操作,由此验证了设计的准确性。文中所搭建SOC系统,可以与符合ARM公司的AHB2.0协议的北斗基带芯片无缝连接,在北斗接收机的设计、测试中有重要的参考价值。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码