基于FPGA/DSP技术的1553B飞机总线系统通讯软件的设计

in: 0px auto; ">④自检测过程。自检测过程是在收到上位机的自检命令后,实现接口板的数据发送 和接收性能测试。

(4)中断控制程序

在DSP芯片TMS320F206接口的设计中,使用3个硬件中断,INT1,INT2由FPGA来产生,INT3 则由上位机来产生。INT1表明FPGA的接收单元已收到一个数据,通知F206读数,INT2表明FPGA的接收单元已收到一个错误数据,通知F206读取错误状态信息,INT3是上位机和接口板数据传输控制的一种手段,通过INT3中断,上位机告诉接口板进行数据接收还是数据发送操作,发送多少数据,采用的消息格式以及总线控制等信息。

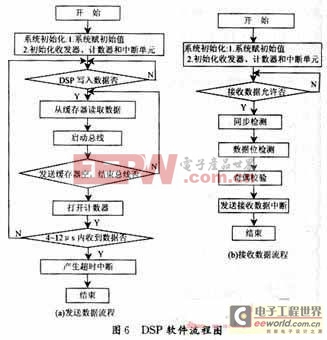

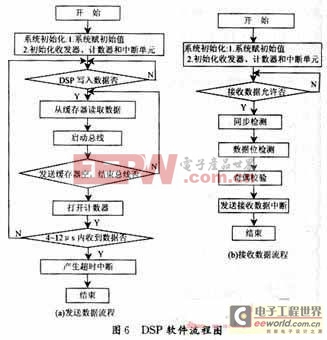

DSP部分的软件采用C++和汇编语言混合编程,关键路径如中断服务程序,数据发送和接收程序都采用汇编语言以达到最大的执行效率,主程序采用C++编写。

DSP部分软件的流程图,如图6所示。

5.3 上位机控制程序

主要实现上位机在特定的操作系统下对接口板的软件驱动、数据通讯和传输控制。主要使用C++在Windows环境下进行软件开发。

6结语

本文介绍了一种基于FPGA和DSP对某型飞机总线系统通讯软件设计与实现的方法。在实际的运用中,较好的实现了总线系统通讯功能,对1553B总线研究具有一定的使用和参考价值。

(4)中断控制程序

在DSP芯片TMS320F206接口的设计中,使用3个硬件中断,INT1,INT2由FPGA来产生,INT3 则由上位机来产生。INT1表明FPGA的接收单元已收到一个数据,通知F206读数,INT2表明FPGA的接收单元已收到一个错误数据,通知F206读取错误状态信息,INT3是上位机和接口板数据传输控制的一种手段,通过INT3中断,上位机告诉接口板进行数据接收还是数据发送操作,发送多少数据,采用的消息格式以及总线控制等信息。

DSP部分的软件采用C++和汇编语言混合编程,关键路径如中断服务程序,数据发送和接收程序都采用汇编语言以达到最大的执行效率,主程序采用C++编写。

DSP部分软件的流程图,如图6所示。

5.3 上位机控制程序

主要实现上位机在特定的操作系统下对接口板的软件驱动、数据通讯和传输控制。主要使用C++在Windows环境下进行软件开发。

6结语

本文介绍了一种基于FPGA和DSP对某型飞机总线系统通讯软件设计与实现的方法。在实际的运用中,较好的实现了总线系统通讯功能,对1553B总线研究具有一定的使用和参考价值。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码