从4004到core i7——处理器的进化史-CPU构成零件-3

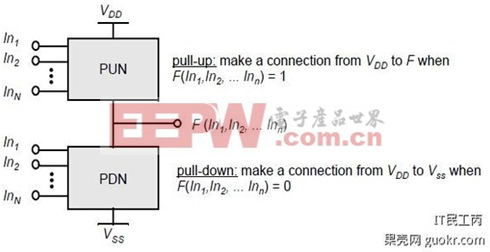

从上面的帖子中我们看到了CMOS工艺下的反相器。如果用一张图总结一下这种设计模式就是下面的这张图

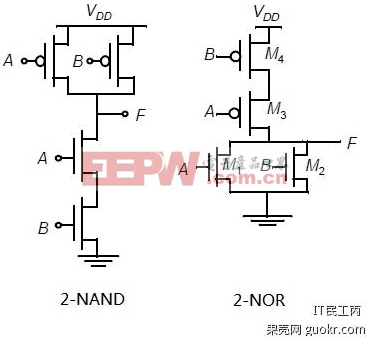

注意,上面的图片中的PUN(pullup network)和PDN(pulldown network)是互补的,也就是说:同一组输入下,要么PUN中存在VDD->输出点的通路,要么PDN中存在输出->地(VSS)的通路,这也正是互补(complementary)的含义。由于不存在由VDD->地的回路,所以CMOS逻辑电路没有静态功耗。我们说CMOS逻辑电路是静态(static)的,即在一组输入下稳定后,输出点是通过一条低阻的(导通的MOS管的电阻大约在10k~100k数量级)通路上拉到VDD或下拉到地的。由于这样的低阻通路是存在的,所以CMOS电路受外界干扰较小,特别受漏电的影响较小(因为电源能向其补充失掉的电荷),这使得CMOS数字电路成为最稳定、最可靠的电路之一。下面我贴两张最常用的逻辑门:2输入NAND和2输入NOR的CMOS实现:

下面的内容是最后的背景知识。

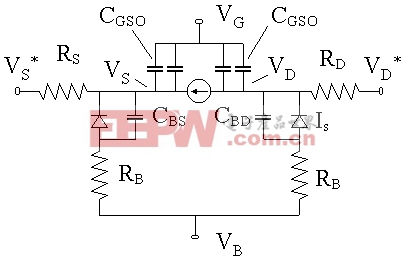

所有以上的分析中我们都在讨论电路的静态特性,即输入稳定相当长的时间后与输出的关系。而在IC的设计中,我们不仅仅关心一个电路功能的正确性(correctness),健壮性(robustness)还关心其性能(performance),即其在单位时间内正确地处理的输入信息量的多少。为此我们不得不引入MOSFET管的一些细节以讨论其动态特性(dynamic behavior),看看下面这张稍显复杂的图。

注意图中的六个电容。这些电容是MOSFET管的寄生参数(parasitic parameter),它们的引入不可避免的,因为相邻的导体之间必然会产生电容。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码