一种新型带宽自适应全数字锁相环的设计方案

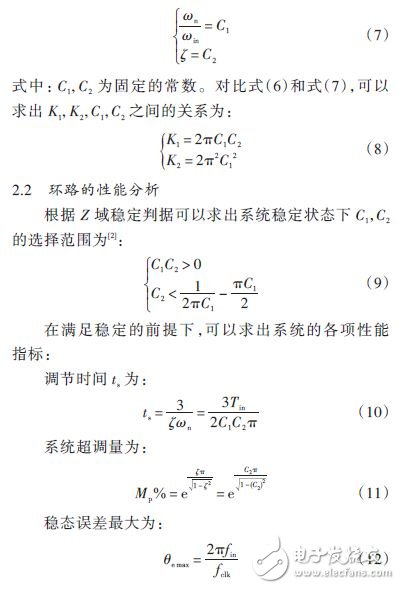

式中:K1、K2 是滤波器的控制参数,ωin 是输入参考信号的角频率。如果令K1、K2 均为固定的常数,那么式(6)满足文献[10]中提出的带宽自适用控制律,即满足下式:

式(10)表明,系统的调节时间和输入信号的周期成正比,这和带宽自适应控制律式(7)一致。根据式(10),(11)可以选择合适的C1, C2 以确保系统良好的动态性能,从式(12)可以看出提高系统高频时钟频率fclk,可以减小系统的稳态误差。

3 系统仿真和试验

本设计采用Verilog HDL硬件描述语言进行电路设计,以Altera公司的Quartus Ⅱ软件为设计平台,最后应用EP1C6Q240C8 FPGA 器件实现硬件电路,其中芯片的系统时钟频率为20 MHz.选取控制参数C1 = 0.113,C2 = 0.707,此时环路滤波器控制参数K1 = 2-1,K2 = 2-2,系统的响应时间ts 约为6 个输入信号周期;超调量Mp%为4.32%;频率跟踪锁定范围设计为76.3 Hz~78.1 kHz.

3.1 仿真波形及分析

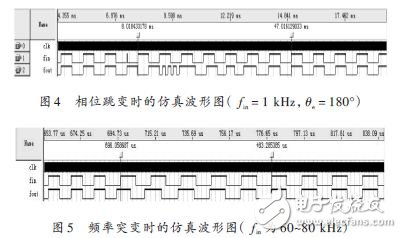

本文所设计锁相环的仿真波形图如图4,图5所示。

从仿真波形图4可以看出,锁相环在输入信号相位发生180°跳变时,可以在7个周期左右实现相位的重新锁定。从图5可以看出当输入信号频率发生突变时,系统也可以迅速地实现重新锁定。

3.2 硬件实测波形及分析

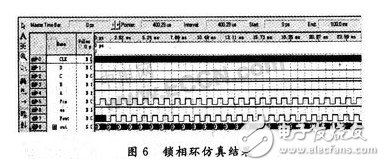

硬件实测波形图如图6所示。

从实测波形图可以看出,系统具有锁相范围宽,稳态误差小等优点。

4 结论

本文提出的基于自适应比例积分复合控制方式的全数字锁相环的设计方案,可实现对环路的实时控制,其自由振荡频率可随输入信号频率的变化而改变,克服了传统锁相环所存在的缺陷。具有电路结构简单、锁相范围宽、锁定速度快、稳定误差小等优点。它可作为功能模块嵌入到数字系统芯片中,具有十分广泛的用途。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码