结构紧凑的超声成像系统连续波多普勒(CWD)设计的挑战

NT: 14px/25px 宋体, arial; WHITE-SPACE: normal; ORPHANS: 2; LETTER-SPACING: normal; COLOR: rgb(0,0,0); WORD-SPACING: 0px; -webkit-text-size-adjust: auto; -webkit-text-stroke-width: 0px">图1. 基于CWD延时线的接收机简化电路

这种架构很容易集成,因为它所需要的电压-电流转换器、模拟开关、无源延时线以及单路I/Q混频器很容易集成。通过配置交叉开关求和,适当的延时线抽头切换信号,达到每个接收器的延时要求。

波束成型后的RF CWD信号混频后得到基带I、Q音频信号,这两路信号经过带通滤波后由高分辨率ADC进行数字转换,用于数字频谱分析。RF至基带的混频处理通常是接收链路保证SNR的瓶颈,这个处理过程对CWD的性能影响较大,以64通道设计为例,I/Q RF混频器需要在处理波束成型信号时具有175dBc/Hz (1kHz频偏)的动态范围。

很难找到或设计能够达到这一指标的混频器,此外,本振驱动信号还必须保持极低的抖动。遗憾的是很难从市场上获得能够达到这样指标的逻辑器件。虽然CWD延时线波束成型器能够满足结构紧凑的超声系统的最低要求,上述性能的局限性也是亟待解决的问题。

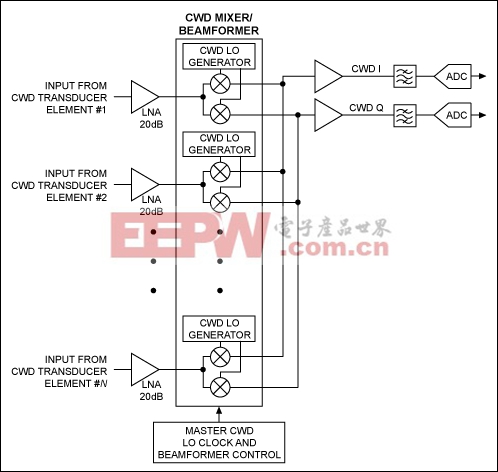

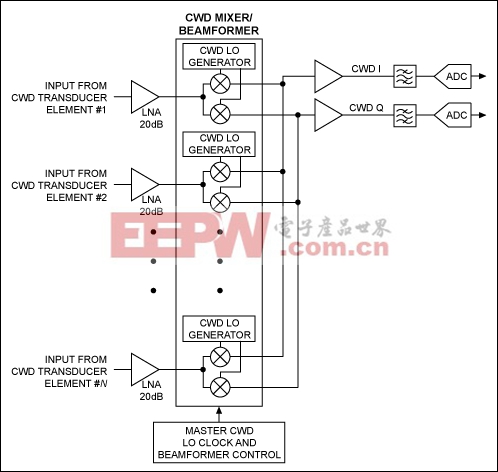

图2. 低功耗双极型LNA和CWD混频器/波束成型电路能够简化高性能CWD接收机的设计

由于混频器的实现基于每个通道,对每个通道混频器的要求可以降低到157dBc/Hz (1kHz频偏)。这一SNR指标虽然苛刻,但利用双极型混频器和标准逻辑器件可以实现。混频器输出为电流,而且在声波基带进行无源求和,可以满足CWD波束成型的SNR要求。

这种架构很容易集成,因为它所需要的电压-电流转换器、模拟开关、无源延时线以及单路I/Q混频器很容易集成。通过配置交叉开关求和,适当的延时线抽头切换信号,达到每个接收器的延时要求。

波束成型后的RF CWD信号混频后得到基带I、Q音频信号,这两路信号经过带通滤波后由高分辨率ADC进行数字转换,用于数字频谱分析。RF至基带的混频处理通常是接收链路保证SNR的瓶颈,这个处理过程对CWD的性能影响较大,以64通道设计为例,I/Q RF混频器需要在处理波束成型信号时具有175dBc/Hz (1kHz频偏)的动态范围。

很难找到或设计能够达到这一指标的混频器,此外,本振驱动信号还必须保持极低的抖动。遗憾的是很难从市场上获得能够达到这样指标的逻辑器件。虽然CWD延时线波束成型器能够满足结构紧凑的超声系统的最低要求,上述性能的局限性也是亟待解决的问题。

基于混频器的CWD波束成型

为了获得更高性能,在CWD系统中引入一个CWD混频器/波束成型器,简化框图如图2所示。该架构中,每个通道都具有一个I/Q混频器,在基带端(而非RF端)进行波束成型求和;每路I/Q混频器的LO相位可以调节在n (n = 8至16相)个相位的其中之一。LO相位的变化将改变接收信号的相位,达到波束成型的目的。

图2. 低功耗双极型LNA和CWD混频器/波束成型电路能够简化高性能CWD接收机的设计

由于混频器的实现基于每个通道,对每个通道混频器的要求可以降低到157dBc/Hz (1kHz频偏)。这一SNR指标虽然苛刻,但利用双极型混频器和标准逻辑器件可以实现。混频器输出为电流,而且在声波基带进行无源求和,可以满足CWD波束成型的SNR要求。

基于混频器的CWD波束成型方案

1 2 3

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码