由开关电源驱动的高速ADC设计

dding: 0px; font-family: 宋体, arial; font-size: 14px; line-height: 25px; ">

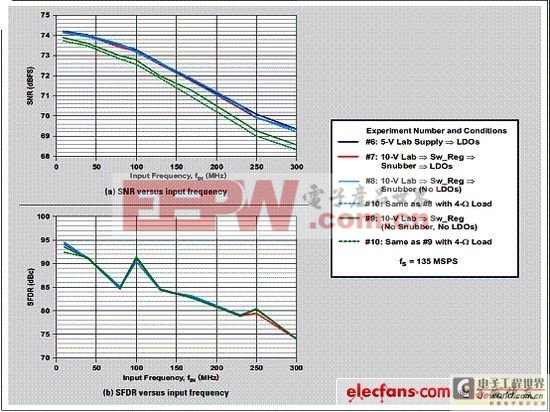

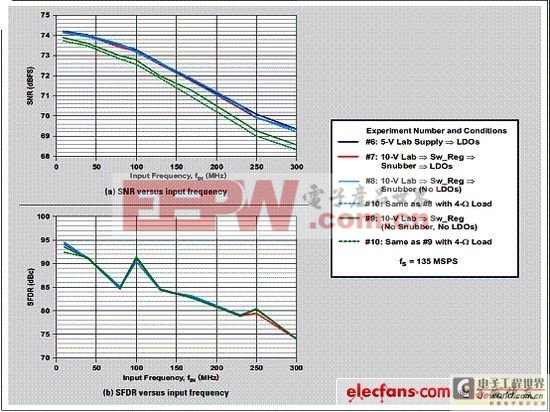

图12:10到300MHz的输入频率扫描。

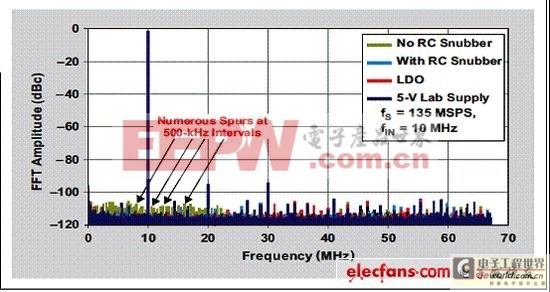

比较图13所示FFT图,我们知道无RC缓衝器SNR稍微减少的塬因。去除RC缓衝器电路后,在ADS6148输出能谱中,我们可看到分佈间隔约为500kHz(TPS5420开关频率)的众多小突波,如图13所示。相较于ADS5483,这些小突波更具主导性,并且因为ADS6148的固有低PSRR SNR大幅降低。但是,图13所示FFT图还显示添加的RC缓衝器电路较好地弥补了这一不足。

图13:大批突波的65k点FFT图。

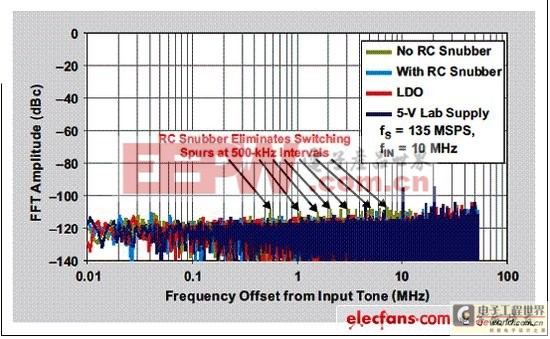

图14所示标準化FFT图显示交换式稳压器的突波高出ADC平均杂讯层约5到6dB。其非常低,以至于其对SFDR减少无法产生影响,但却明显地影响了ADC的SNR。

图14:标準化FFT图显示使用RC缓衝器的好处。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码