集成电源噪声抑制的时钟源简化FPGA系统的电源设计

图1(a)的小数分频拓扑图是由一个晶体振荡器、模拟鉴相器、模拟补偿滤波器、模拟VCo和一个小数分频反馈分频器组成。输出频率等于输入频率的N倍。低噪声缓冲器用于驱动外部负载电路。许多应用程序,例如千兆以太网、光纤通道以及高清晰度串行数字视频(HD-SDI)信号,依靠输出频率在100Hz~156.25MHz范围的低抖动时钟源。在理想的供电条件下,小数分频PLL可在1 0kHz~20MHz频段内提供低于lps RMS的抖动性能。相反,在有电源噪声的环境中,振荡器很难满足其数据手册中标明的相位抖动参数。使用模拟子电路构建的节点非常敏感,极易受到噪声的影响。当噪声进入系统,它通常会放大并输出相位抖动。

6 Silicon Labs DSPLL时钟产品解决方案

相比之下,Silicon Labs DSPLL使用数字处理技术实现PLL,通过倍乘晶体参考频率得到更高的输出频率,晶体不会受到干扰。其次,所有频率控制和增减使用数字命令进行处理。补偿滤波器基于数字信号处理器,没有使用电容器或其他被动元件。最后,VCo使用数字控制,而不是模拟电路。为了提供额外的VDD隔离,片上线性稳压器和集成的电源去耦电容用来进一步确保噪声抑制。由于这些优势,即使在嘈杂的环境中,每个Silicon Labs的基于DSPLL技术的XO/VCXO都有能力产生具有亚皮秒级抖动性能的高频时钟信号。

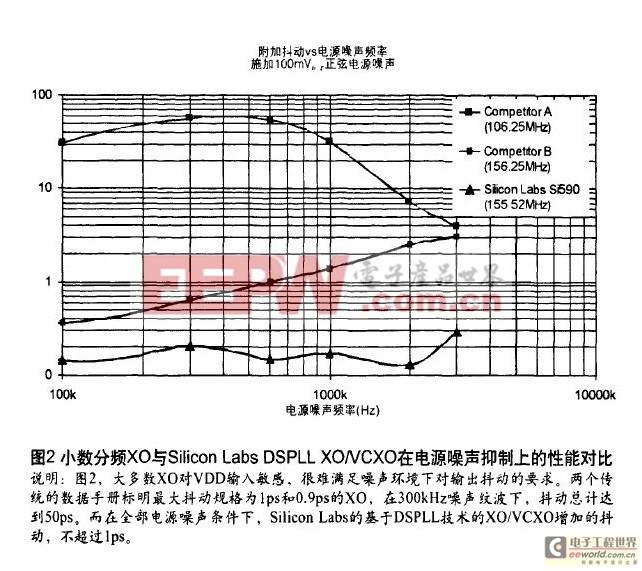

图2所示为基于小数分频PLL的xo与基于SilicOrlLabs DSPLL的Xo在电源噪声抑制上的性能对比。虽然基于小数分频PLL的振荡器被证明可达到最大0.9ps RMS的抖动性能,满足高数据率FPGA SERDES的要求,但是这只适用于理想环境下。在100mV,,的电源噪声下,竞争对手的解决方案增加了多达40ps RMS抖动,无法满足高速串行链路要求。而SiliconLabs的基于DSPLL技术的XO/VCXo产品依旧满足要求,在所有测试频率点上,仅仅影响。增加了0.1ps RMS~0.3ps RMS的抖动。

7 结语

在实际应用中,当前面向FPGA的设计需要对电源开关噪声有更大抗干扰能力的时钟。SiliconLabs基于DSPLL技术的时钟和振荡器家族是高性能应用FPGA的理想选择,它们既满足高速串行链路对低抖动性能的要求,又通过集成电源噪声抑制能力,使实际条件下的操作最优化

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码