模拟前端(AFE)原理及选型指南

Silicon Labs的C8051 F350采用“多数字,少模拟”设计,这是公司最新推出的带片上ADC的8051兼容MCU。它集成有8通道24位100ksamples/s转换器、50MHzCPU。外设包括双8位DAC和温度传感器以及串行通信外设(UART,SPI,SMBus串行口)。

同样,Microchip 公司的PIC16F684、PIC16F688和PIC12F683 PIC基MCU 包含10位连续渐近ADC和8输入多路转换器。

更为复杂的是Cypress公司的pSoC家族,具有一组复杂的数字和模拟单元,完全可以电路内重新编程。一个pSoC IC模拟单元可包含多达4个ADC(6~14位分辨率,可选择流水线、Δ-Σ和连续渐近架构);2、4和6极带通、低通和陷波滤波器;6~9位DAC;PGA。pSoC设计工具包括2个预配置Δ-Σ转换器模型。一个具有8位分辨率,64X过取样并适合32ksamples/s。另一个具有11位分辨率,256X过取样,适合7.8ksamples/s。

在AFE中采用内插设计相对较简单,因此,将该功能内插到AFE中较为可取,并简化了数字主机芯片对其进行的输送。这也意味着芯片间的接口可以更低的速率工作,清除了可能的电磁干扰源。

ADI公司的AD9862是一款双12/14位、128Msamples/s ADC,带有取样滤波器和数字Hilbert滤波器。当滤波器使能时,它执行一次Hilbert转换,将单通道输入数据分解为I和Q分量,用做图像抑制结构部分。然后,用片上数字复杂调制器对复杂数据做进一步处理。某些AFE也可能包括直接数字合成和数字混频器,所以在接收通道,D-S转换内含数字滤波。D-S转换在窄带无线应用中特别有用,因为它具有高选择性和非常高的瞬时动态范围。

根据转换器结构进行设计的工程技术人员可能会惊奇地发现,D-S转换采用的频率达到几兆赫兹。开始,D-S应用目标是高分辨率、慢速响应应用(如称重);后来应用到音频领域。工艺的进步使得D-S结构将取样速度增加到20Msamples/s,使有效带宽增加到2.5MHz,同时提供16位有效分辨率。

另一方面,尽管D-S转换在窄带无线应用(通过分立PF信道的语音通信)中颇具吸引力,但是,其架构不适于宽带应用。相反,连续渐近转换器通常用于工业控制和测量中的高速带宽应用。现在,16位300Msamples/s连续渐近转换器较为普遍。

流水线转换器成本较低,可用于只需8位或12位分辨率和10Msamples/s转换率的应用。流水线架构导致等待时间,但具有较高的芯片处理效率。一个12位流水线转换器需要4095个比较器和一个大芯片,导致芯片功耗很高。

相比较而言,通过分级转换,流水线转换器所需要的比较器数量大大减少,但要以牺牲6个或7个等待时间周期为代价。等待时间只是反馈控制系统中的一个潜在问题。在通信系统中这不是问题,因为转换器的等待时间对于整个信号链络的延迟来说是微不足道的。

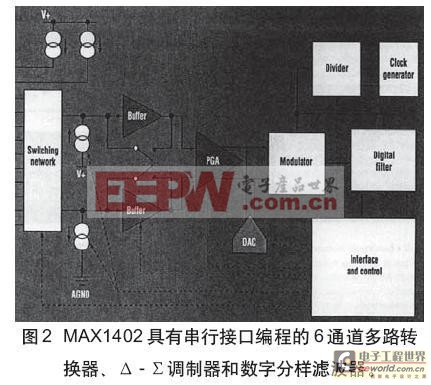

在此之前,人们曾讨论过插入式滤波器放在DAC之前的原因。尽管Maxim公司的MAX1402在D-S转换器之后包含一个分样滤波器,但不会在流水线ADC的输出有一个分样滤波器。从经济角度看,在采用价廉ADC时可以在模拟域加入一个表面声波滤波器和另外滤波器。

1 2 3

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码