基于FPGA的可配置FFT_IFFT处理器的设计与实现

2.4 乒乓RAM设计

为了满足无线移动通信要求,实现对连续数据流和突发数据流的处理,本文设计的FFT/IFFT处理器采用了输入、输出双乒乓结构,保证了系统高吞吐率的要求。设计共使用4组RAM(RAM0~RAM3),每组RAM划分为4块存储器。输入数据写入RAM0组中的4块存储器,写完后开始写入RAM1,与此同时,从RAM0组中读出数据送入蝶形单元进行计算,其结果按照同址计算规则写回相应的地址,直到M级蝶形运算完成后,最终的计算结果写入RAM2。RAM2写满后,即可从RAM2读出计算结果,同时RAM1组中的数据将被读出送入蝶形单元进行运算,其运算结果按照同址运算规律送回RAM1存储,M级蝶形运算完成后,最终结果写入RAM3组,RAM3写满后即可从中读出运算结果。

2.5 无冲突并行地址设计[4]

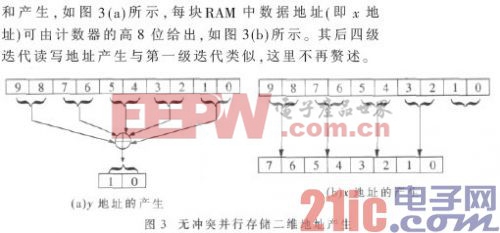

4路并行数据处理结构需要保证每次读取的一组数据分别存储在不同的RAM中,否则在数据读取时会产生地址冲突[5]。本设计中RAM地址采用二维地址,其中地址x表示每块RAM中数据地址,y表示数据来自RAM块的标号。

3 FPGA实现及测试分析

本文FFT/IFFT处理器采用Verilg硬件语言描述,在Mentor公司的Modelsim仿真平台上进行了RTL功能仿真及时序仿真,其结果与Matlab仿真结果进行比较显示正确。处理器采用了Xilinx 公司Virtex-Ⅱ xc22v500 芯片进行了验证,在SMIC COMS 0.18 ?滋m工艺下对设计的处理器进行了综合仿真。结果显示:完成64点16 bit符号数复数FFT运算只需要50个时钟周期,完成256点FFT运算需要256个时钟周期,最大时钟频率可以达到167 MHz,处理器的单元核心面积为1.4 mm2。设计完全满足了无线移动手持终端设备高速小面积的设计要求。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码