全功能SPI接口的设计与实现

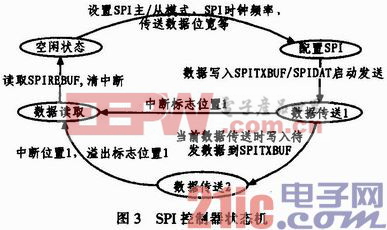

写入SPICRR寄存器里的Char0~Char3位将会配置SPI状态控制模块里的计数器。状态控制是系统的核心部分,为了使系统结构化,设计了状态机,如图3所示,分为3种状态,分别是空闲状态、发送命令状态(配置SPI各个寄存器)、数据状态。其中数据状态包括数据的传送和读取。

作为全功能SPI接口,在设计时加入了测试模块。使能相关地址译码,将使系统内部关键节点通过输出控制模块传送到数据总线。

2.3 全功能SPI控制器的时钟设计

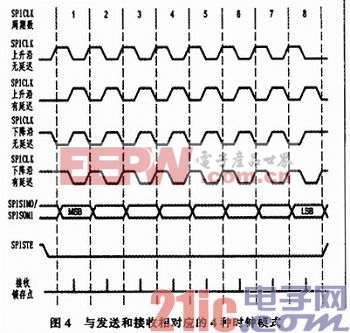

SPI控制器为了和外部数据进行交换,根据外设工作要求,其输出串行同步时钟极性和时钟相位可以进行匹配。但时钟极性对传输协议没有重大影响。如图4所示,全功能SPI控制器包括4种不同的时钟模式:

无延时的上升沿:SPI在SPICLK信号上升沿发送数据,在SPICLK信号下降沿接收数据;

无延时的下降沿:SPI在SPICLK信号下降沿发送数据,在SPICLK信号上升沿接收数据;

有延时的上升沿:SPI在SPICLK信号上升沿之前的半个周期发送数据,在SPICLK信号下降沿接收数据;

有延时的下降沿:SPI在SPICLK信号下降沿之前的半个周期发送数据,在SPICLK信号上升沿接收数据;

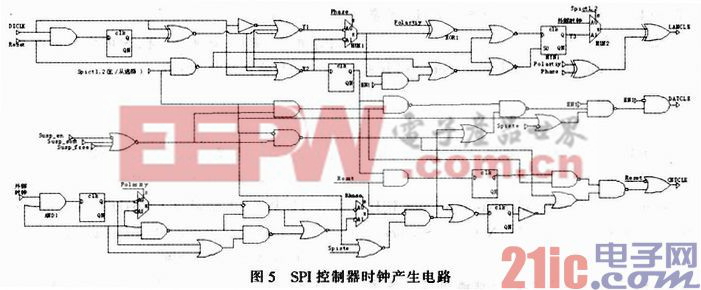

对于SPI控制器内部时钟的产生,在对系统时钟进行分频之后,还要对生成的时钟进行一定处理,因为分频后的时钟其高电平时间是几个系统时钟周期的和,控制移位寄存器的时钟采用的是系统时钟,为了在SPICLK的一个时钟周期内只移位一位数据,必须要求内部时钟的高电平时间为一个系统时钟的周期,才能保证在SPICLK的一个时钟周期内,只有一位数据的接收和发送。

图5为实现上述功能的具体电路,即SPI控制器时钟产生的电路结构。在图5中,分频后的时钟为DICLK,作为与门的一个输入端进入模块后对其进行处理。节点Y1和Y2的输出方程为:

分频时钟DICLK通过节点Y1和Y2后,其高电平时间仅为一个系统时钟周期,且Y1较Y2延迟半个周期。MUX1的选择端S来自配置寄存器的Phase端,选择有延迟的Y1还是无延迟的Y2通过。分频后的时钟将被用于两个用途,一是产生SPICLK作为从控制器的输入时钟。二是作为主控制器的内部时钟,被用于计数器的计数脉冲和用于控制串行移位寄存器SPIDAT。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码