一种34位串行编码方法的设计及其FPGA实现

在单极性归零码合成模块中,信息“1”和信息“0”分别送到D触发器的预置端和清零端,经过D触发器处理后,产生单极性归零码信号(Sd)。将单极性归零码信号送入到34位串入并出移位寄存器模块中,在移位时钟的作用下,单极性归零码信号在串入并出移位寄存器模块内逐位移动,形成34位并行码,并由锁存脉冲(Latch)锁存并行数据,校验位验证模块对并行数据进行模3校验位验证,当校验位正确时,产生确认脉冲,作为嵌入式控制器SPOC模块的中断信号,SOPC模块响应中断并执行中断服务程序,读出并行数据,存储在存储器中。

串入并出移位寄存器模块由FPGA芯片的LPM_SHIFT-REG(移位寄存器)兆功能实现。校验位验证模块用到了LPM_DIVIDE(除法)和LPM_COMPA RE(比较器)兆功能。

SOPC模块设计基于NiosⅡ软核嵌入式微处理器,利用FPGA 中的可编程逻辑资源和IP软核可以方便地构成嵌入式微处理器的接口功能模块,SOPC模块包括NiosⅡ处理器、Avalon交换式总线、片内外存储器以及外设模块等。根据需要,可对NiosⅡ嵌入式系统裁剪,进行自己定制。SOPCBuilder软件自动生成Avalon总线,用户可以将处理器、存储器和其他外设模块连接起来,形成一个完整的系统。在本部分电路设计中,用到了NiosⅡ嵌入式处理器的片内存储器和中断功能。

在接收模块设计中,应着重考虑如何找到34位串行编码的起始位,这也是保证接收模块可靠性的关键。由于两个相邻码位的时间间隔为一个码位周期,所以可以采用计数超时方法对移位脉冲进行串行编码起始位检测,寻找起始位。起始位检测模块主要由计数器构成。超时门限的设定原则上应大于一个码位周期,而小于两个码位周期。该模块的输入时钟来自分频模块的32 MHz高稳定晶振。分频后的输入时钟为16 MHz,即以串行编码传输速率20倍的频率进行超时计数检测。

具体电路实现还要考虑串行信号传输时产生的信号畸变等因素,上述门限设定原则应有所冗余。从接收到一个码位到设定的时间门限之间,如果没有接收到其他码位,则可认为即将到来的下一个码位就是一个34位编码的起始位,此时将串入并出移位寄存器做清零处理,每接收完一个34位串行编码都应重新找一次起始位。从可靠性考虑,设计了移位时钟脉冲完整性检测电路,这样,即使接收偶尔出现误码,也不会影响其他34位串行编码的接收。

2.2 34位串行编码的发送

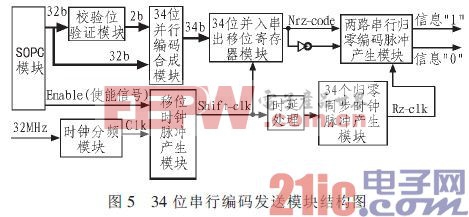

进行34位编码发送时,需要将所发送的32位并行数据转换为带有校验位的34位并行数据。SOPC模块将32位并行数据送入到校验位运箅模块,计算出两位校验位,32位并行数据与两位校验位送入34位并行编码合成模块,合并成34位并行编码。SOPC模块发出使能信号(Enable),使能移位时钟产生模块,该模块产乍移位时钟脉冲(Shift-clk),移位时钟脉冲经过时延电路后,产生归零同步时钟脉冲(Rz-clk)。

在移位时钟脉冲的作用下,34位并行数据在并入串出移位寄存器中逐位移出,形成两路极性相反的非归零串行编码(Nrz-code),与34个归零同步时钟脉冲相或后,即产生信息“1”和信息“0”的单檄性归零脉冲。单极性归零脉冲经电流驱动电路后,送入耦合变压器输出。在编码发送模块设计时,需要注意归零同步时钟脉冲与非归零串行编码的时序控制,防止出现“毛刺”信号,这可以采用触发器延时的方法实现。34位串行编码发送模块结构图如图5所示。

3 结束语

某专用接口装置采用34位串行编码与外部设备进行信息交换,该编码具有抗干扰性强,可靠性高的特点,适用于电磁环境恶劣情况下的信号传输。在该专用接口装置检测设备研制中,采用以FPGA芯片为核心的可编程逻辑设计以及SOPC软核设计技术实现了该类型编码的接收、发送电路。试验表明:设计的34位串行编码收发模块可靠性高,即使在文际测试信号有比较明显畸变的情况下,收发也未出现错误,功能完全满足要求,能够实现专用接口装置的接口功能检测。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码