基于FPGA和ARM9的片上网络系统硬件平台

2.2 阻抗匹配设计与仿真

输出缓冲的源端内阻、高速系统中传输线的特征阻抗以及输入缓冲的输入电阻间的差距带来了信号传输过程中的反射。当输出门的信号在传输介质上往返时间大于信号最小边沿时间时,电路需采取端接来实现阻抗匹配,端接可采用末端并接电阻或源端串接电阻等方式。

末端端接将电阻放置于接收器端一侧,驱动波形沿传输线以满幅度传播,到达末端时由端接电阻吸收,接收电压等于传输电压。末端端接具有上升时间快的优点,但对输出门的驱动电流有一定的要求,这也带来了较大的功率消耗。

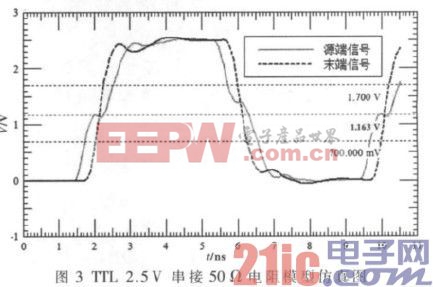

源端端接采取控制输出端的反射系数的方法。通过在源端串接一个电阻,使得串接电阻加上源端缓冲器的内阻接近传输线的特征阻抗。Cyclone IV系列产品均设计了OCT功能,可以选择使用片内串接电阻。使用SigXplorer软件首先提取PCB上AD9765数据线的传输线模型,然后与Altera提供的TTL 2.5 V串接50 ?赘电阻的IBIS模型进行125 MHz信号的反射仿真,仿真结果如图3所示。源端信号波形的幅度由于端接电阻的分压,在传输介质上的初始信号幅度降至满幅度信号的1/2,这1/2幅度的信号大约经过1 ns后到达末端。由于末端数字电路输入阻抗非常大,反射系数接近+1,从而得到1/2幅度的反射信号,与原1/2幅度信号叠加后在末端得到完整幅度的信号。反射信号再经过1 ns延迟后回到源端,被源端端接衰减,此类端接具有静态功率小等优点。

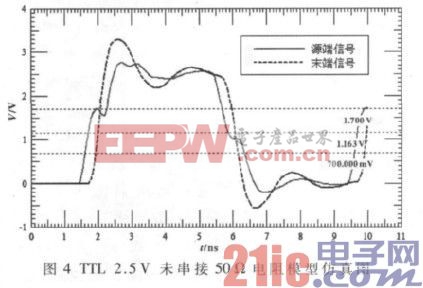

同时对未串接50 ?赘电阻的TTL 2.5 V 模型进行了仿真,其它仿真参数均不变的情况下,发现电路末端信号具有明显过冲现象,如图4所示。因而Cyclone IV的OCT技术是简化高速线路PCB板设计、提高信号完整性最简便实用的途径。实验表明,测量结果与仿真波形接近,AD9765在最高理论速度125 MHz下工作稳定。

2.3 串扰仿真

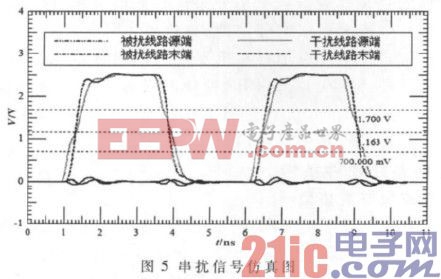

互感、互容使得相邻传输线间信号相互耦合从而形成串扰,传输线的间距是其中最关键的因素。本系统中大多数走线间距为15 mils,无需担心串扰问题,而BGA的扇出采用的是5 mils的间距, 并且存在许多长度在1 000 mils以上的平行线,串扰的仿真与降低串扰的影响成为设计过程中不可缺少的一个环节。采用SigXplorer对相邻BGA扇出微带线的模型进行了仿真,结果如图5所示。干扰源是125 MHz的时钟信号,被干扰线路为相距干扰线路5 mils的弱下拉平行微带线。可见在被扰线路的源端和末端产生了接近200 mV的串扰,属于电路正常工作可以接受的范围。

设计了基于FPGA的NoC系统硬件平台,在此基础上完成了一个小型的片上网络系统。设计过程中充分考虑了片上网络系统的应用特点,针对典型3×3的2D Mesh结构进行设计。实践表明,系统达到了设计要求,可以满足NoC系统的硬件要求,同时系统也将作为后续NoC映射、路由及测试算法的验证与仿真平台。

NoC仍然有着广阔的研究空间,许多新的结构或算法将会不断涌现,以及更复杂应用系统的验证需求对硬件平台会有更高的要求。本文对平台设计中一些重要的问题进行了探讨, 对于后续相关硬件平台的开发及FPGA应用系统的设计具有一定的借鉴意义。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码