基于FPGA的IRIG-B标准DC code编码器VHDL设计

摘要:为了实现靶场时统终端输出IRIG-B标准DC code信号,采用VHDL语言在FPGA逻辑电路中设计了DC code编码器硬件电路,通过QuartusⅡ软件建立工程文件对VHDL语言DC code编码器电路进行编译和仿真,获得了符合IRIG-B标准的DC code信号。经过实践验证,该电路具有实现方法简单、电路稳定性好、精度高的特点,实测同步精度小于1μs。

关键词:IRIG-B;DC code;FPGA;VHDL

O 引言

在测控设备的时间统一系统向靶场试验系统提供标准时间和频率信号,以实现整个试验系统的时间和频率的统一,是由各种电子设备组成的一套完整系统。时统设备阁向用户设备发送的时间信号中,含有时间信息编码的串行时间码,该码应与标准时间精确同步的时间信号,适用于信道传输。IRIG(Inter Range Instrumentation Group)是美国RCC(Range Commanders Council)所属的负责制定靶场标准等工作的机构,由其所属TCG负责,制定了靶场时统和通信系统的标准。IRIG时间标准包括并行时间码格式和串行时间码格式,IRIG-B码是串行时间码格式,是我国标准化时统设备与用户设备接口的时间信号标准的基础。

1 IRIG-B标准DC码

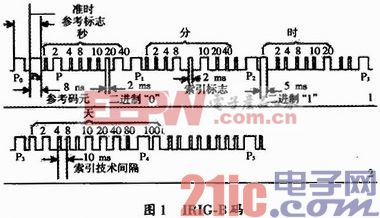

IRIG-B码的帧频是1帧/s,每一帧包括100个码元(脉冲),每个码元的准时参考点是该脉冲的前沿。IRIG-B码采用脉宽调制的方法表示,码元的脉冲宽度有3种,每种脉宽代表各自不同的信息,分别为脉宽2 ms代表二进制“0”、脉宽5 ms代表二进制“1”、脉宽8 ms代表该码元为标识位。一帧IRIG-B由100个码元组成,从参考码元PR开始到位置识别标志P0结束。参考标志是由位置识别标志P0和相邻的参考码元PR组成的,PR的前沿即为该帧B码的准秒时刻。在一帧B码中,每10个码元中有一个位置标示符,被记作P1,P2,P3,…,P9,P0。如图1所示。

每帧中表示时间信息的码元共有30个,时间信息采用二-十进制编码,它所表达的时间包括:从00~59共7个码元的‘秒’信息、从00~59共7个码元的‘分’信息、从00~23共6个码元的‘时’信息、从001~365或366共10位码元的‘天’信息。帧中还有特标控制等信息。所有未携带信息的码元其宽度均为2 ms。

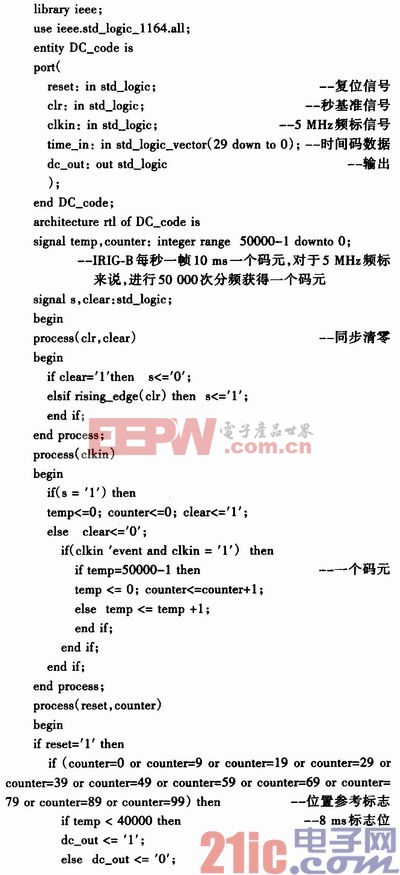

2 VHDL语言实现

VHDL语言实现程序如下:

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码