基于PCI总线的嵌入式实时图像处理系统

DSP完成的功能主要是对从FIFO读入的数据进行处理,包括依照程序进行识别、特征提取以参数检测等。当视频头采集速度为每秒25帧图像时,它留给DSP处理的时间最多为每帧40ms,如果考虑系统中一定的延时以及处理后图像的存储时间,那么DSP处理一幅图像时间不能超过30ms,按照C6211的处理速度,在30ms内可以处理36M条指令。DSP读出FIFO中的行数据并存入SDRAM,一帧图像有576行,在最后一行时会收到帧中断,这时SDRAM中的图像数据总共有1440×576=810KB。让C6211用36M条指令的时间处理810K的数据是绰绰有余。

(2) SDRAM存储器

HY57V651620B是现代公司发布的128Mb SDRAM,支持分页寻址,访问速度为7.5ns,与DSP系统同步工作,但因为DSP工作在150MHz,故系统中SDRAM工作在DSP时钟的一半或者2/3,即75MHz或者100MHz。当工作在100MHz时候,SDRAM在时序上需要一些特殊的控制,不是简单的与DSP同步。SDRAM主要在系统运行过程中存储临时数据和处理结果。系统中共有256Mb的存储空间,其消耗情况视启动程序和图像处理程序的大小而定。

(3) FLASH存储器

AM29LV800B是AMD公司发布的8Mb FLASH芯片,同样支持分页寻址,工作在异步方式。启动程序固化在FLASH芯片中。当系统加电启动时,FLASH中的程序下载到DSP的SDRAM中运行。FLASH具有在线重写入功能,这对系统启动程序的修改和升级都带来了很大的方便。

2.2 视频解码模块

本系统视频A/D采用的是Philips公司的SAA7111A作为视频解码芯片,SAA7111A可以提供四路模拟视频输入,具有两个模拟处理通道,支持四路CVBS模拟信号或二路Y/C模拟信号或(2×CVBS和1×Y/C)。SAA7111A对视频头输入的标准PAL格式的模拟图像信号进行A/D转换,然后输出符合CCIR601建议格式的4:2:2的16位YUV数据到FIFO,其中亮度信号Y为8位、色度信号Cr和Cb合为8位数据。FIFO采用的是IDT公司的IDT72V215LB芯片,深度为512×18。按照CCIR601标准,YUV图像分辨率为720×576,那么按行输出时,SAA7111A输出数据流大小为:720×16=1440bit。因为DSP通过32位的SBSRAM接口与FIFO通信,故YUV数据写入FIFO时需要在FIFO之间实现乒乓切换,这时一行720×16的数据在两片FIFO中存储变为360×32。

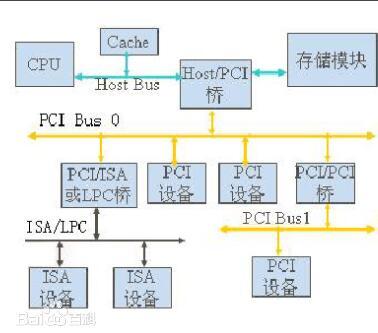

2.3 PCI通信模块

PCI(Peripheral Component Interconnect,外围组件接口)它既可以作为中间层的总线也可以作为周边总线系统使用。与其他普通总线规范相对照,PCI总线为高速I/O设备提供了更好的支持,比如可以很好的支持图像适配器、网络接口控制器、磁盘控制器等。现行的标准允许在33MHz下使用64根数据线,传输速率可达2.12Gbps。并且PCI总线支持线性突发的数据传输模式,可确保总线不断满载数据,因此能有效利用总线带宽。另外,PCI总线还具有低延时的随机存取特性,对从总线上的主控寄存器到从属寄存器的写延时为60ns。

PCI总线规范吸引人的地方不仅是其高速度,更在于它适应了现代I/O设备对系统的要求,对PCI扩展卡及器件能进行全自动配置,并且只需很少的接口逻辑就可以实现并支持其他总线系统。

TMS320C6211的HPI口不支持PCI总线的无缝接口。本系统中采用TI公司的PCI2040来实现DSP的HPI与PCI总线的连接。DSP处理后的数据经HPI口输出到PCI2040进行解码,然后输出到PCI总线上。其逻辑结构图如图3所示。

在本系统中,PCI2040上存在2种电压:5V和3.3V,其中3.3V是HPI口电压,而5V是PCI总线电压。PCI2040在启动时需要对其PCI总线寄存器和HPI寄存器参数进行预加载。系统中PCI解码模块包括一块配置ROM--AT24C08A,属于EEPROM型ROM,便于对配置参数的修改和升级。当系统启动时,存储在AT24C08A的数据被下载到PCI2040的寄存器中并进行配置。

图中/HINT[3:0]、/HCS[3:0]、HRDY[3:0]、HRST[3:0]分别与4片DSP中的相应信号相连,即PCI2040可以同时与4片DSP接口。

3 PCI总线驱动实现方法

在系统软件方面,基于PCI总线的图像处理系统面临的难点颇多,其中难度最大的是PCI驱动问题。

为阐明如何在Windows操作系统下实现PCI总线的驱动,还需了解PCI设备的配置空间系统。PCI设备有3种物理存储空间:配置空间、存储器空间和I/O空间。配置空间是长度为256字节的一段连续空间,空间的定义如图4。在配置空间中只读空间有设备标识、供应商代码、修改版本、分类代码以及头标类型。其中供应商代码用来标识设备供应商的代码;设备标识用来标识某一特殊的设备;修改版本标识设备的版本号;分类代码用来标识设备的种类;而头标类型用来标识头类型以及是否为多功能设备。除供应商代码之外,其他字段的值由供应商分配。基地址寄存器最重要的功能是分配PCI设备的系统地址空间。在基地址寄存器中bit0(最低位)用来标识存储器空间还是I/O地址空间,基地址寄存器映射到存储器空间时bit0为“0”,映射到I/O地址空间时bit0为“1”。

3.1 Windows环境下驱动程序

驱动程序可以理解为一系列控制硬件设备的函数。在Windows操作系统中,封装驱动程序的方法是制作一个DLL或VxD。当硬件是非标准设备时,必须针对特定的硬件来设计Windows环境下的设备驱动程序。

在DOS操作系统,对于一个应用程序而言它总认为自己是唯一运行的程序,因此应用程序可以直接访问硬件,独占所有的系统内存以及系统运行时间,当然也就不需要设备驱动程序。但到了Windows操作系统,系统中同时可能有若干个应用程序在运行,这就使得系统不可能让它随意的直接访问硬件,否则就会引起应用程序访问冲突而导致系统崩溃。为解决这一问题,人们提出将系统的资源虚拟化,让应用程序运行在一个虚拟定环境中的虚拟机(VM)上,而管理程序和驱动程序运行在实际机器上(Ring0级),由它们来处理针对硬件的操作。虚拟资源是硬件(甚至软件)资源的仿真,当系统虚拟了所有或者几乎所有的程序可以访问的资源时,它就创造了一个“虚拟机”(VM)。Windows虚拟机完全透明的仿真了以下资源和性能:

(1) 可访问的内存空间

(2) I/O操作

(3) 中断操作

(4) 外围设备(显示器、键盘等)

如此以来,Windows应用程序在Ring3级(最低级)的保护模式上运行,不能直接访问硬件,执行一个对硬件的操作就会引起一个异常事件,此时处理器切换到Ring0级,并且将控制权交给相应当控制器。所有Windows应用程序分享一个系统虚拟机。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码