从头到尾构建混合信号高集成度系统(SoC)的步骤(6):布局

Dave:我们可能知道这个工艺设计过程,但有些事情是可变的:金属层的数量可能变化,为了得到一个高阻值的电阻我们可能需要做另外一次的植入和掩膜步骤。另外还可能有一个在软件中自动布局的大数字电路区。所以每个项目都有一个不同的组合。

Tamara博士:我想成本会随着层数的增加而上升,那么我们为什么使用比方说四层而非三层金属层。

Dave:这取决于芯片。如果我们有更多互连层、更多金属层,那么数字电路封装的尺寸就要小得多。所以,如果数字区很大,那么多加一层金属会使芯片更小,其效益足以弥补附加层的成本。

Tamara博士:所以该工作是为了优化整个工作而不只是层数。

Dave:是。事情总是这样。

Tamara博士:还有没有其他事情与此类似?你提到了需要另一个植入步骤来得到一个高阻值的电阻。你能否使用较低阻值的电阻和串联多个来获得你要的高阻值电阻。

Dave:能行。但如果电阻面积增加,它会增加寄生电容并可能使高频电路性能下降。同时始终存在成本权衡:高值电阻占用面积小,在一些特别的设计中可以节省足够多的硅片面积来补偿附加植入步骤所产生的成本。

Tamara博士:面积似乎常常被提到。我想它是设计最基本的约束条件和成本动因之一。那么这些器件的相对大小如何。CMOS晶体管与电阻或电容比较起来怎样?

Dave:我要给你一个典型的工程学答案:这取决于其他条件。晶体管可非常小,在数字设计中通常是这样。但在模拟设计中,一对晶体管需要匹配,这意味着它们需要是大尺寸,或至少足够大。电阻尺寸可以小到典型模拟晶体管的尺寸和大到芯片晶圆面积的一半,这取决于设计。作为比较,1k-10k电阻是几个典型模拟晶体管和几十个数字晶体管的尺寸……大致是这样。电容尺寸大,可以说是太大。我根据RC和有源放大器构建了许多滤波器,电容是模块中最大的元件完全不是什么不寻常的事情。你还记得741运算放大器吗?

Tamara博士:当然。常用的单位增益稳定741:我使用了成百个此种放大器。

Dave:嗯,741运算放大器中的单个最大器件是30pF补偿电容。

Tamara博士:有意思。所以你想不使用电容。

Dave:不使用多余的电容。

Tamara博士:你提到了匹配。似乎像提到面积一样多。这怎么处理?

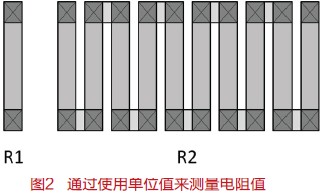

Dave:许多电路性能都依赖于值的比率而非绝对值。例如模/数转换器、数/模转换器和带隙基准等。在这些模块中,我们想让关键值是彼此的整数倍。我们通过使用单位元件来做到这一点:我们构建电阻、电容甚至大晶体管,作为通用小元件的集合。这样,我们知道R2是R1大小的10倍,因为R2是10个单位R1串联起来的,而R1只是其中一个。请看图 2。

Tamara博士:哇!这样,我们知道它是完美的……

Dave:不完全是。芯片发热可能不均匀,所以电阻中的所有元件可能并不全是同一温度,这会使它们不匹配。我们用几何学方法解决该问题。例如,在带隙电路中,我们可能想让一个晶体管是另一个晶体管的8倍。所以我们先在芯片上放一个晶体管,然后在它周围放8个完全相同的晶体管。这样,如果整个模块有温度差异,一些器件的温度可能稍高,一些可能稍低,但周围8个器件平均下来会几乎与中央器件一样。我们称之为公共质心方案。有许多与此相似的诀窍。

Tamara博士:看来这要等到下次来讨论了。但至少我们“清理”了你的咖啡。真是够乱的,是不是?

Dave:是。嗨,谢谢你停下来帮我……下次也许我们可以擦一擦我的窗户!(全文完)

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码