基于FLEX10K50与CPCI总线的脉冲信号检测系统设计

2.2脉冲信号接口

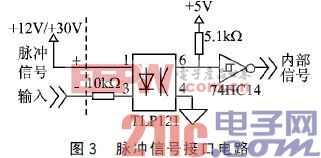

被测脉冲信号为功率驱动信号,用于驱动功率负载,驱动电流通常为几mA至几百mA,采用集电极开路门(OC)形式输出,通常为+12~+30 V信号。为了兼容多种信号电平,并能隔离功率型信号与普通基带电平信号,实现较好的电磁兼容性,本系统采用光电耦合器作为信号隔离与电平转换的接口器件。

TLP121是东芝公司生产的光电耦合器,隔离阻抗为MΩ级,其前向驱动电流(IF)最大为20 mA,后端开关开启和闭合时间均为μs级,可以满足本系统对测量误差不大于1 ms的要求。输入接口电阻设为可调电阻,可适应不同输入电压。

脉冲信号接口电路如图3所示。脉冲信号正线和回线连接至光耦的前端(图3中TLP121的1、3引脚),后端(图3中TLP121的4、6引脚)采用板内5V电源上拉,通过施密特电路74HC14整形后发送至接口处理FPGA.当脉冲信号有效时,光耦前端有电流流过,接口电路输出高电平“1”;脉冲信号无效时,接口电路输出低电平“0”。

2.3接口处理

FPGA由于需要对80路脉冲信号进行检测,采用单片机无法满足并行处理的需求,因此选用FPGA完成脉冲采样功能。接口处理FPGA采用Altera公司的FLEX10K50,工作主频为6 MHz,存储芯片采用EPC1PC8.其主要功能有三部分:分频定时器、采样数据缓存、外围控制逻辑。FPGA对主时钟进行分频,形成周期为1 ms的时钟信号。FPGA每ms对80路脉冲信号完成并行采集一次,将数据存放在寄存器中,同时向单片机发出中断信号,通知单片机发起数据搬移,以及单片机内部的时间计数器自增。采样数据缓存模块用于将80路脉冲信号同时锁存至内部寄存器,单片机每ms全部读取一次。外围控制逻辑用于单片机外围各控制信号的译码,包括控制寄存器、各芯片控制信号译码,以及其他辅助功能的实现。

2.4单片机系统

单片机系统采用Atmel公司的AT89C51,配合32KB外部SRAM 62256以及4 KB双口数据RAMIDT71342.其中,CPCI总线访问双口数据RAM的L端口,8051访问R端口。

单片机工作主频设计为20 MHz.单片机P0口和P2口作为通用的数据线和地址线使用,配合地址锁存器74HC373工作;P1口不使用;P3口中仅使用了P3.2用于接收外部中断,即来自接口处理FPGA的中断。FPGA内部定时器每ms产生一个中断脉冲,用于单片机软件计时器的激励时钟,同时通知单片机读取脉冲信号接口采样数据。

单片机的外部地址空间划分如表1所列。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码