基于ARM+FPGA的运动控制器设计与实现

3.1 FPGA 内部关键功能模块设计

FPGA 不擅长对数据进行运算处理,但本系统对每个轴的控制都要进行相应的运算,因此在每个轴的控制模块设计中尽量不涉及复杂的算法实现,算法部分留给ARM 进行处理。原则上FPGA 仅仅接收经ARM 进行处理过的数据,而后按照ARM 主控单元的处理结果进行处理。

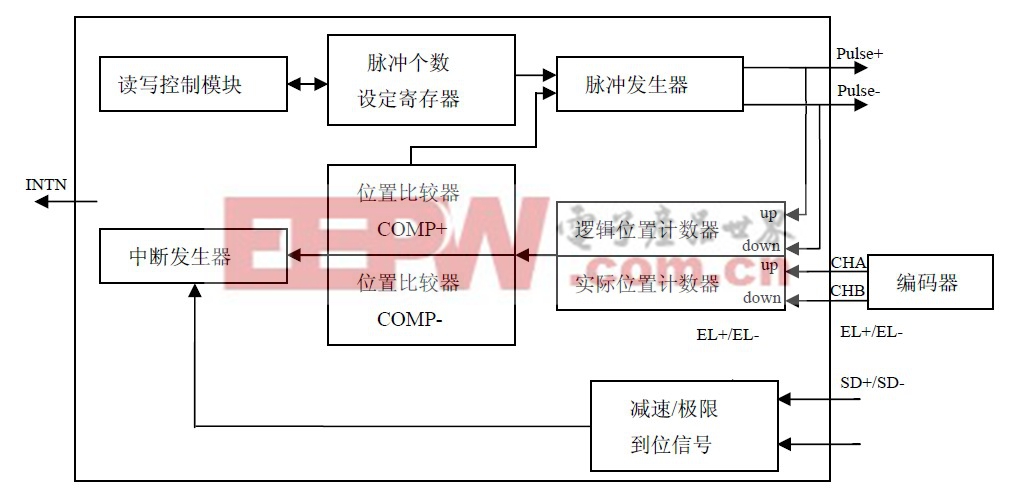

单轴控制模块框图如图3 所示。在每个位置管理单元中都配置了两个计数器:逻辑位置计数器和实际位置计数器。其中逻辑位置计数器的输入端接到脉冲发生器的输出端,其功能是计量从脉冲发生器实际发出的脉冲数量。实位计数器的输入端接到编码器的输出端,其功能是计量从编码器发出的脉冲个数。逻辑位置寄存器和实际位置寄存器实际上构成一个闭环系统,前者为闭环系统的输入,后者为闭环系统的输出。当两者的误差范围不超过某一个限度时,在FPGA中对实时的脉冲发送速率进行调节;当两者的误差超过某一个设定的范围时,FPGA 向ARM 发送一个中断请求。当某个轴接收到减速信号SD 或者极限到位信号EL 时,在FPGA 内部经过同样一个中断发生器模块向ARM 发送一个中断。ARM 接收到中断信号后,开启运动控制进程,对PID 控制参数进行整定,计算控制量。

图3 单轴控制模块设计

3.2 驱动程序接口设计

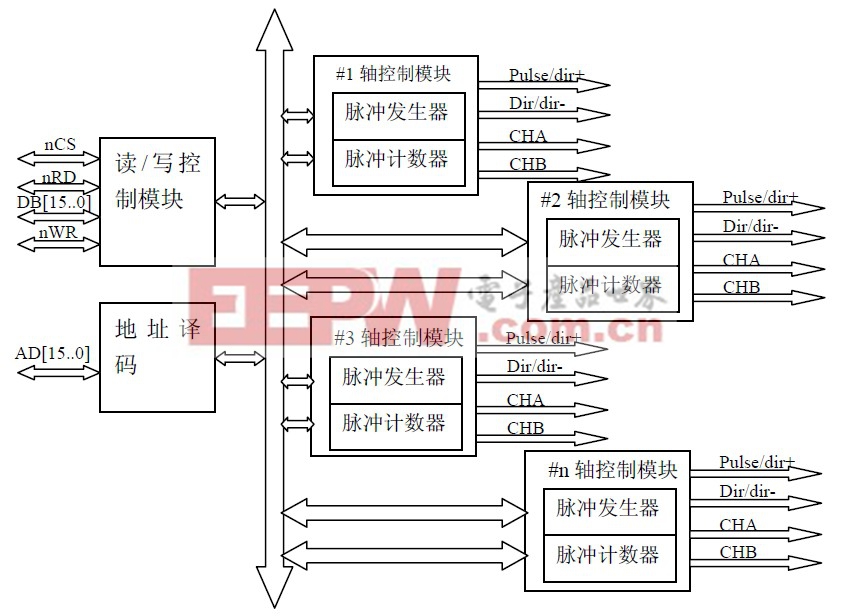

在系统设计中,两片FPGA 作为ARM 的外设,挂在ARM 的外设地址空间。当ARM 要访问FPGA时,首先要在ARM 中运行包含FPGA 所在地址空间地址的指令,而后ARM 的片选线选中FPGA,FPGA检测到自己被选中,从而开始检测地址总线上传来的ARM 指令所包含的地址数据。根据从ARM 地址线传来的地址总线上的数据,FPGA 读取从ARM 数据总线上传来的数据总线上的数据,而后开始进行相应的动作,从而完成一次控制任务。寄存器是本运动控制系统的基本组成部分之一,ARM 对FPGA 的控制就是通过配置在FPGA 内部的寄存器来实现的。完成配置的FPGA 整体结构如图4 所示。

图4 FPGA 内部结构图

4 控制算法设计与仿真

4.1 单神经元自适应PID 控制器设计

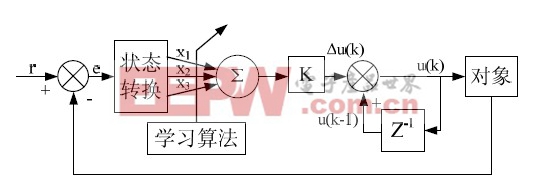

单神经元自适应PID 控制器的结构如图5 所示。

图5 单神经元自适应PID 控制器

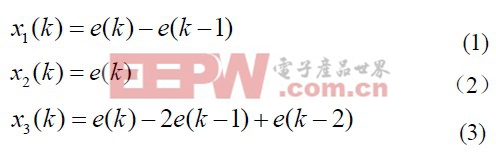

图5 中,神经元的3 个状态变量分别为:

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码