双余度DSP数据采集装置在某型控制器中的应用

3.2.2 IDT7133的访问冲突控制

使用双口RAM的关键是需要对其进行逻辑仲裁,否则可能会导致数据访问冲突。当控制器同时读写双端口RAM IDT7133时,可能存在以下两种情况:

(1)无冲突的访问控制

当两个端口的地址不相同时,在两个端口上进行读写操作一般不会发生冲突。此时任一端口被选中,就可对整个存储器进行存取,每一个端口都有自己的片选控制和输出控制。IDT7133无冲突的读写控制真值表如表3所列。其中,L表示逻辑低;H表示逻辑高;X表示无关。

也只有一个输出低电平,不会同时输出低电平,从而保证至少有一个端口能进行正常访问。其判断方式有以下两种:

第一种是判断:如果地址匹配并且在信号之前有效,片上的控制逻辑在和之间进行判断来选择端口;

第二种是地址有效判断:如果信号在地址匹配之前有效,片上的控制逻辑在左、右地址间进行判断来选择端口。

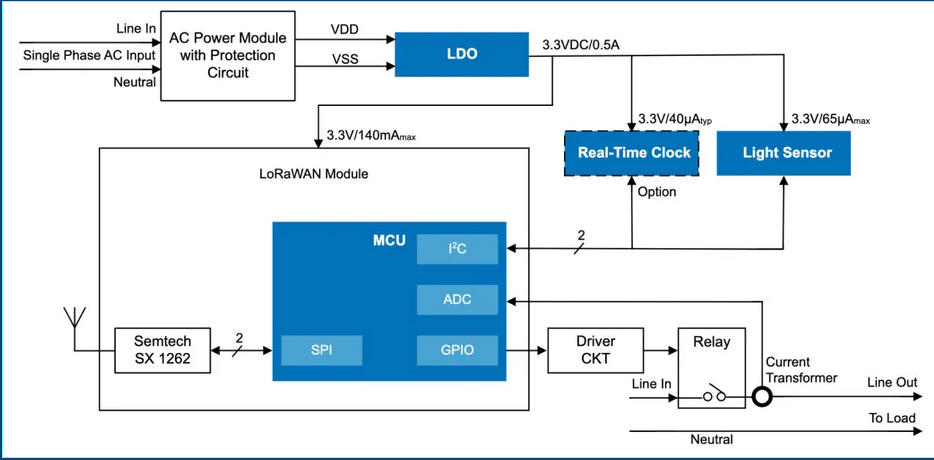

3.3 数据交换模块的设计

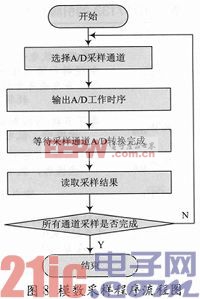

本控制器DSP间的数据通信采用双端口RAM的通信方式的电路框图如图6所示。该电路通过两个译码电路分别产生左侧端口的控制信号R/WLUB、R/WLUB、在启动信号的上升沿开始转换。转换结果采用查询方式读取,当查询到EOC引脚输出低电平时,DSP发出读信号将数据读入。此时该通道的A/D采样完成,下一个周期进行另一个通道的采样,直到所有通道的采样完成为止。

图8所示是其模数采样程序流程图。

5 结语

本文针对某型控制器的需求,分别设计了以DSP为核心的数据采集模块,并采用双端口RAM方式构建了数据交换模块,从而很好地解决了因数据传输速度低所引起的瓶颈问题,文中同时给出了模数采样程序流程图。经验证,本系统可以达到预定功能,具有一定参考价值。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码