基于TMS320C64x 的MPEG-4实时编码器设计与实现

信息时代对于视频通讯的需求越来越广,从较低码率的可视电话、视频会议、实时监控到高码率的空中侦察、数字电视等,迫切要求将高效率、高质量的视频压缩算法实用化。MPEG-4于2000年正式成为国际标准并不断地扩展。它不仅支持码率低于64kbps的多媒体通信,还能支持广播级的视频应用。与以前的视频标准相比,MPEG-4可以提供更高的压缩效率、更好的交互性以及更强的抗误码能力。目前,MPEG-4已经成为视频压缩标准的主流。

MPEG-4算法非常复杂,其编解码的实时性难以保证,通常只能实现对中低分辩率视频的实时编码。本文基于TI公司的C64x系列DSPs设计并实现了一种MPEG-4编码器,实现了对D1分辨率(720×576)视频的实时编码,且在保证输出码率低于1Mbps的同时,解码图像具有较高的峰值信噪比和较好的视觉效果。

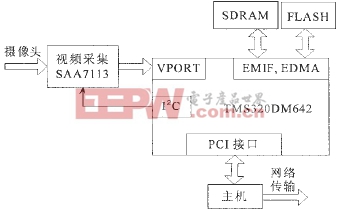

1 编码系统的硬件结构

编码系统以TMS320DM642高性能通用DSP芯片为核心。图1为系统框图。

图1 编码器系统框图

1.1 TMS320DM642芯片的特点

DM642属于TI公司的C64x系列DSPs。Veloci TI结构使C6000 DSPs在视频和图像处理中得到广泛应用。CPU的VLIW结构由多个并行运行的执行单元组成,这些单元在单个周期内可执行多条指令。并行是C6000获得高性能的关键。C64x在C6000的基础上有一些重要的改进。除了有更高的时钟频率外,C64x从以前的Veloci TI结构扩展到Veloci TI.2结构,包含了许多新的指令,增加了额外的数据通道,寄存器的数量也增加了一倍。这些扩展使得CPU可以在一个时钟周期内处理更多的数据,从而获得更高的运算性能。

DM642芯片集成了各种片内外设,使得开发视频和图像领域的应用更为方便。它带有三个可配置的视频端口,提供与视频输入、视频输出以及码流输入的无缝接口。这些视频端口支持许多格式的视频输入/输出,包括BT.656、HDTV Y/C、RGB以及MPEG-2码流的输入。利用DM642开发视频编码器,其视频输入部分只需要一块视频采集芯片即可,如Phillips的SAA7113,无需外加逻辑控制电路和FIFO缓存,使硬件系统更为简单和稳定。DM642的其它外设包括:10Mbps/100Mbps的以太网口(EMAC)、多通道音频串口(McASP)、外部存储器接口(EMIF)、主机接口(HPI)、多通道缓冲串口(McBSP)以及PCI接口等。

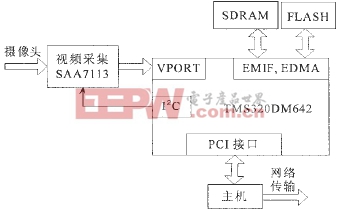

1.2 系统工作流程

该编码系统可分为图像压缩卡和主机两部分。其工作流程如图2所示。

图2 系统工作流程图

MPEG-4算法非常复杂,其编解码的实时性难以保证,通常只能实现对中低分辩率视频的实时编码。本文基于TI公司的C64x系列DSPs设计并实现了一种MPEG-4编码器,实现了对D1分辨率(720×576)视频的实时编码,且在保证输出码率低于1Mbps的同时,解码图像具有较高的峰值信噪比和较好的视觉效果。

1 编码系统的硬件结构

编码系统以TMS320DM642高性能通用DSP芯片为核心。图1为系统框图。

图1 编码器系统框图

1.1 TMS320DM642芯片的特点

DM642属于TI公司的C64x系列DSPs。Veloci TI结构使C6000 DSPs在视频和图像处理中得到广泛应用。CPU的VLIW结构由多个并行运行的执行单元组成,这些单元在单个周期内可执行多条指令。并行是C6000获得高性能的关键。C64x在C6000的基础上有一些重要的改进。除了有更高的时钟频率外,C64x从以前的Veloci TI结构扩展到Veloci TI.2结构,包含了许多新的指令,增加了额外的数据通道,寄存器的数量也增加了一倍。这些扩展使得CPU可以在一个时钟周期内处理更多的数据,从而获得更高的运算性能。

DM642芯片集成了各种片内外设,使得开发视频和图像领域的应用更为方便。它带有三个可配置的视频端口,提供与视频输入、视频输出以及码流输入的无缝接口。这些视频端口支持许多格式的视频输入/输出,包括BT.656、HDTV Y/C、RGB以及MPEG-2码流的输入。利用DM642开发视频编码器,其视频输入部分只需要一块视频采集芯片即可,如Phillips的SAA7113,无需外加逻辑控制电路和FIFO缓存,使硬件系统更为简单和稳定。DM642的其它外设包括:10Mbps/100Mbps的以太网口(EMAC)、多通道音频串口(McASP)、外部存储器接口(EMIF)、主机接口(HPI)、多通道缓冲串口(McBSP)以及PCI接口等。

1.2 系统工作流程

该编码系统可分为图像压缩卡和主机两部分。其工作流程如图2所示。

图2 系统工作流程图

关键词: TMS320C64x MPEG-4 实时编码器

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码