使用Eye Doctor II工具分析解决测试着色难题

在信号完整性测试中,由于探测点受限引入的传输线延迟,及芯片的寄生参数,会导致测试波形在边沿上有台阶或回沟。这种因测试引入的这种差异叫做测试着色,测试着色引入的信号质量问题一般不用解决,但如何分辨测试着色是一个难题。

LeCroy公司高级信号完整性分析软件包Eye Doctor II提供的VP@RCVR(接收端虚拟探测)功能可以非常方便地利用大家所熟悉的端接模型对这种测试难题进行分析,能够简单快速的分辨测试着色问题,提高硬件调试效率。

测试着色案例

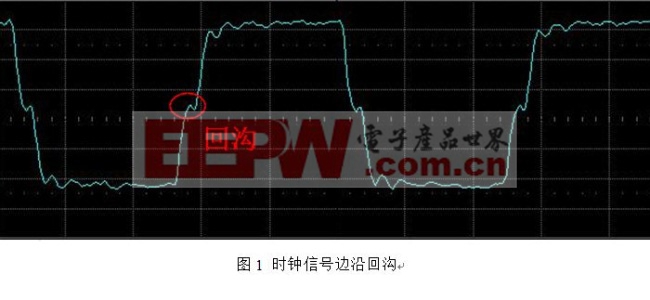

如下波形可以看到该时钟信号边沿出现回沟,这种现象随着信号速率变高而越来越普遍,如何分析这种现象?我们可以通过仿真驱动芯片模型和电路拓扑,检查PCB中参考平面的完整性、信号走线的间距来排除设计问题。如何进一步验证分析是否是测试着色引入的?是否真正满足芯片的指标要求?

下面以该问题作为案例介绍分析过程。

反射的基本原理分析

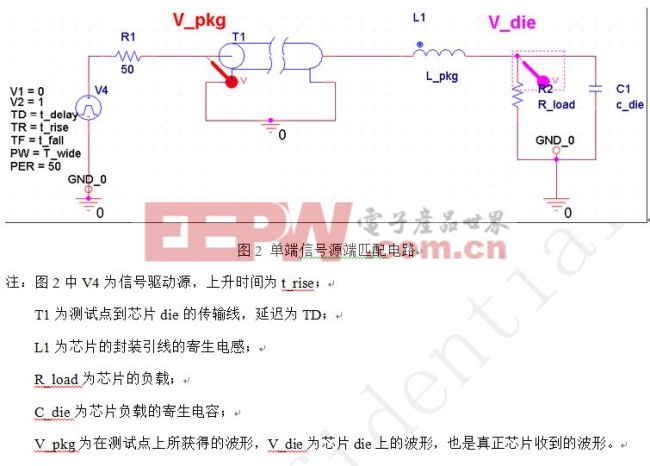

单端的时钟信号以及边缘敏感信号,常用源端串阻来吸收反射。这种拓扑设计理想状况下,源端反射系数为0,负载端的反射系数为1。

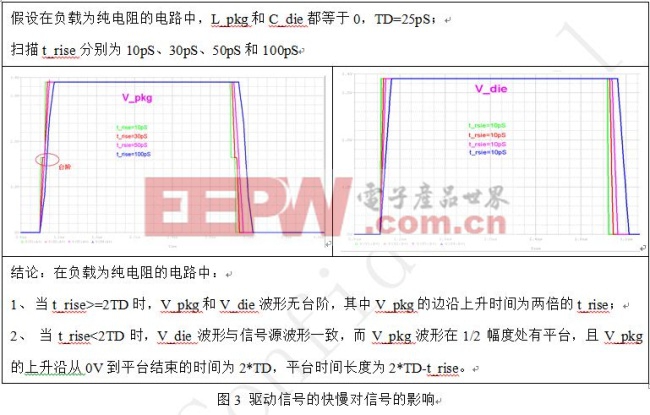

驱动信号的快慢t_rise对V_pkg和V_die的影响:

根据传输线的反射原理,当信号上升时间大于两倍传输线延迟时,则在信号跃迁完成之前,信号探测点处会先完成发射叠加。因此当上升时间小于两倍的传输线时延(TD)时,上升时间将对波形产生严重的影响。

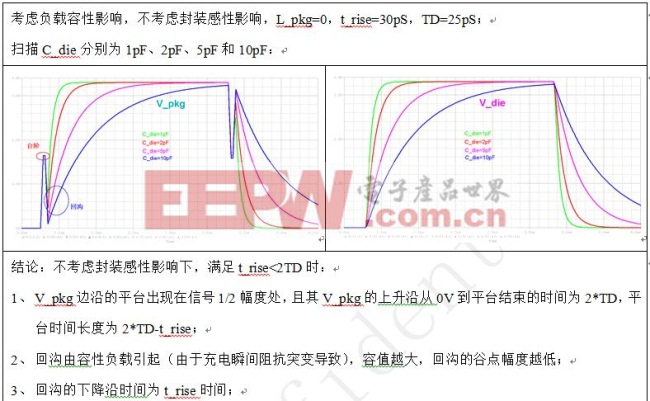

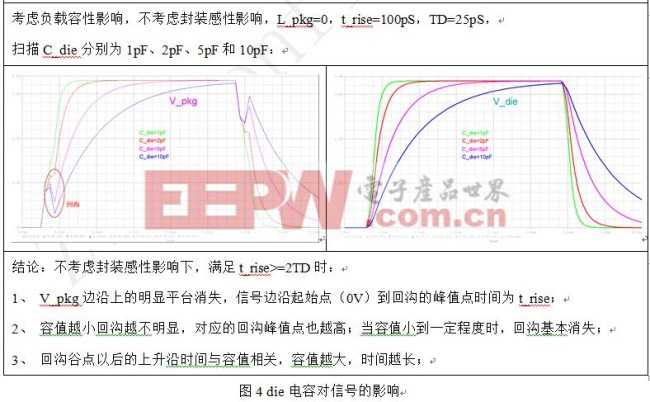

C_die的大小对V_pkg和V_die的影响:

而在实际系统中,几乎没有负载为纯电阻的情况,比如:CMOS门电路的输入大多是呈容性的,而封装的焊接线和框架则是感性的。当传输线端接为容性负载时,驱动器和负载处的波形将与典型的传输线相应波形完全不同。本质上,电容是一种与时间有关的负载,当信号刚到达电容时,电容可看作短路负载,对应的反射系数为-1;电容充满电后,可看作开路负载,对应的反射系数为1。

L_pkg的大小对V_pkg和V_die的影响:

当传输线上的电气通路中出现串联电感时,该电感同样是与时间有关的负载。当电路中刚加上一个阶跃电压时,电感几乎没有电流流过,这会反射系数为1。电感的大小决定反射系数1能保持多长时间,如果电感足够大,信号幅度将会倍增。此后电感释放能量,其放电速度取决于LR电路的时间常数t=L/Z0(Z0为传输线阻抗)。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码

相关文章

-

-

-

-

-

2024-03-28

-

-

-