自适应导通时间降压电路的虚拟ESR环路设计

5 实际电路设计验证

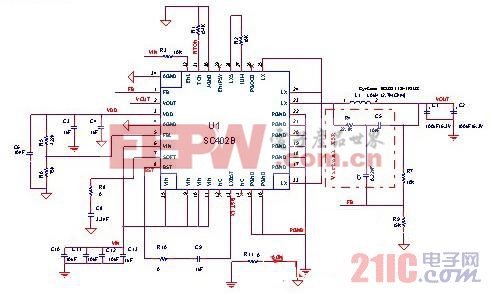

使用Semtech的ECOSpeed系列产品SC402B做一个设计实例,用来验证VESR电路理论的正确性。SC402B是一个支持10A输出的高性能降压调整器。FB需要纹波值最小为10mV。

设计实例的参数为:输入12Vin;输出1Vout/10A; 输出电容是全陶瓷电容设计;工作模式为强制连续。

图 6 实例电路

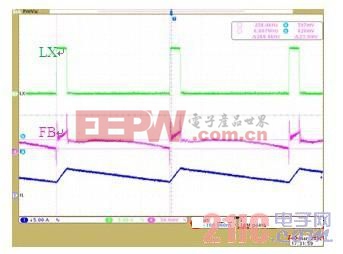

通过前述方式计算得到FB的交流纹波值为15mV,实际测量值为23mV。 实际测量波形如图7所示。

图 7 实例电路测量波形

6 结语

本文主要介绍了虚拟ESR电路的设计方法,并在实际电路上进行了验证。

参考文献

[1] 升特半导体有限公司, SC402B产品数据手册, www.semtech.com

[2] 升特半导体有限公司, Power Management – Constant Ontime Architecture High Current Converter, www.semtech.com

作者简介

毛敏,(1980- ), 男, 汉族, 工程师, 本科, 2003年毕业于浙江大学电气工程学院, 现在升特半导体(深圳)有限公司担任应用工程师。 主要负责升特半导体有限公司电源产品的技术支持和应用。■

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码