兼容51指令的8位MCU IPCORE设计

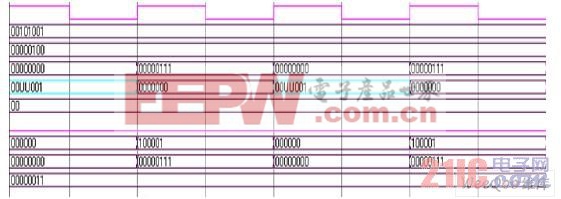

利用Mentor Graphics 的工具MODELSIM SE/对模型进行了模拟验证。此处仅给出了一个简单的指令执行后的模拟结果(见图4)。图中所示为ADD A RN指令的波形图,可以看出,模拟结果与指令执行结果一致。该模型也通过了MODELSIM的可综合性检查。

图4 指令ADD A RN 执行结果

5.2 时序测试

在时序测试中我们选用了ALTERA 公司的不同系列FPGA 芯片来对次IPCORE 进行综合,综合后的性能如下表所示:

从上表我们可以看出虽然不同的器件综合后的结果不相同,但是本文设计的8 位MCUIPCORE 可以完全可以容纳到一个相对门数为20 万门以上的FPGA 中,并且具有较好的时钟频率特性。

6 结论

虽然这里只设计了一款八位的MCU IP CORE,但我们所提出的架构和模块设计新思路可以推广到16位、32位以及64位MCU的设计中。因为不管是多少位的MCU CORE,设计中需要重点考虑的架构以及指令系统基本上是一致的,所不同的只是一些总线位数以及寄存器的位数而已。当然随着位数的增加,一些验证和测试的复杂度也将显著增加,但从设计思路的角度来讲,它们是一样的。在具体的推广中,要根据应用领域的不同,对这些方法进行适当的取舍或适当的改进,以更加符合某些具体应用领域的要求。

本文创新点:本文设计了一种新结构的兼容51指令的MCU IPCORE。设计中引入了纯组合的ALU单元,增加了并行乘除法器,重新设计了外围组件,在设计控制单元的时候,重新设计了指令的时序,并且把指令状态机的时序和组合部分分开设计,提高了状态机的执行效率。从结果上看,时钟频率提高了很多,可由用户根据需要选择合适的ROM和RAM 的大小,并且完全可以把此核放在一个相对门数在20万门以上的FPGA的中。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码