基于的实时控制模块设计与实现

1.2 总线及I/O控制的设计

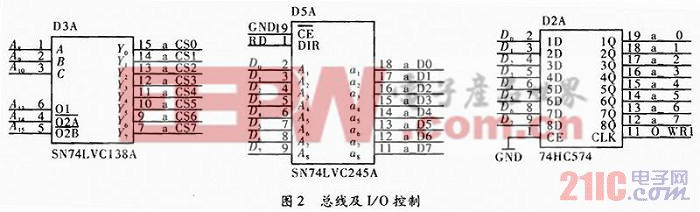

对于射频接收频综、射频发射频综模块,直接采用总线控制,为避免不同的模块控制时相互干扰,用3—8译码器对总线地址译码,产生不同模块的片选信号。同时数据线通过总线收发器以提高带负载能力。对于滤波组件、射频输入/输出等用I/O控制的模块,并未直接使用51芯片的GPIO引脚,则是将数据总线经锁存后模拟GPIO信号供相关模块使用,如图2所示,其中,IO_/WR1由B_/CS7与单片机写线逻辑或后产生。

1.3 SPI及RS232控制接口

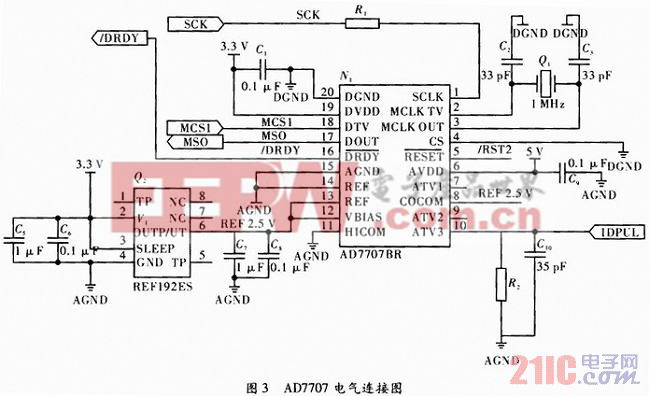

C8051F120芯片上本身自带了A/D转换器,但只有12位,不适合该系统的需求,故在片外另加一片ADI公司的AD7707。其分辨率为16位,是∑-△体系结构,转换的是输入电平的平均值。三通道,输入电平范围可达±10 mV~±10 V。根据实际要求,该系统使用AIN3高电平输入端口,Unbuffered模式,HICOM、REF-接模拟地,VBIAS与REF+均接+2.5 V参考电压,模拟电源5 V,数字电源3.3 V,能检测输入范围为0~10 V的单极性电平。其控制接口是同步串行口,用51芯片的SPI直接控制。图3是AD7707的电气连接图。

单片机与上位计算机的通信使用通用异步收发器UART,外接MAX3224,将UART信号转换为RS-232信号进行传输,MAX3224在3~5.5 V低电压下工作,却可产生RS-232的±12 V电压,只需连接Tx、Rx和地线即可实现异步串行通信。系统中仍有一些时钟、复位电路和电源等,在此不再赘述。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码