基于FPGA的数字中频接收和恢复系统设计

3 AD9957接口设计

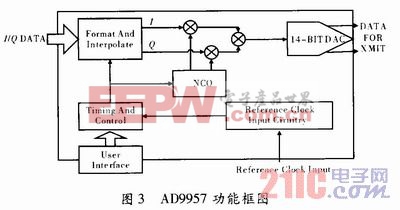

AD9957是正交数字上变频器(QDUC)系列中的第3款产品,其将一个高速、直接数字频率合成器(DDS)、一个高性能高速14位数模转换器(DAC)、时钟乘法器电路、数字滤波器和其他DSP功能集成在一个芯片上,可以在有线或无线通信系统中为数据传输提供基带上变频。AD9957有3种基本的工作模式:QDUC模式、插值DAC模式和单音模式,系统需要用到QDUC模式,如图3所示。

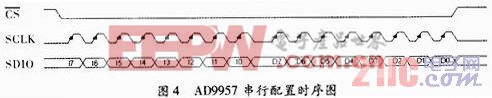

3.1 串行接口设计

AD9957的配置是通过同步串行通讯端口实现的,可以方便地与多种工业用微处理器接口连接,并兼容多种同步传输格式。本设计通过在FPGA内部编写同步串行通讯逻辑实现对AD9957的配置。其串行通讯周期分为两个阶段,第一阶段是传输指令阶段,将指令字写入AD9957,指令字主要包括要访问的寄存器地址,以及将进行的数据传输是读操作还是写操作。第二阶段是数据传输阶段,将数据从串行端口控制器向串行端口缓冲区传输数据,传输的Byte数取决与要访问的寄存器。其时序控制图如图4所示。

3.2 并行接口设计

AD9957有一个18位的并行数据输入端口,在QDUC模式下,FPGA将I/Q数据基带数据交替的输入到AD9957内部。基带数据的时钟PDCLK由AD9957提供,最高支持250 MHz的并行数据时钟,同时也是并行数据的采样时钟。系统中PDCLK工作在200 MHz。AD9957在TxENABLE的上升沿准备接收第一个I字,在PDCLK的有效沿上,第一个I字被锁存至器件,PDCLK的下一有效沿锁存一个Q字,依次类推。需要特别注意的是:确保向器件中送入偶数个数据,因为器件必须捕捉到一个I字和一个Q字,然后才能使接收到的数据沿着信号链处理。

值得注意的是,AD9957的并行数据传输速度较高,容易发生调制数据时序问题,会导致I/Q基带数据相位不平衡等问题,严重时,会导致调制数据错误。因此,在进行硬件设计时,需严格按照AD9957的并行数据传输时序要求操作,必要时在FPGA内部对时序进行优化,以提高数字正交调制器的调制效果。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码