基于DSP/BIOS的多信号并行处理软件架构设计

3.2 系统层

系统层设计为软件架构设计的关键点,充分利用DSP/BIOS提供的调度模块和同步模块。将控制层中的指令解析、交换控制和交换表更新模块与PRD绑定,周期检查有无新指令,并根据指令解析更新交换表,调度周期由32位实时逻辑时钟控制。将控制层中的交换控制和数据交换模块与TSK绑定,根据从其他模块收到的信号量SEM或者邮箱信息MBX,进行数据格式转换,完成不同格式的数据在不同信道间的透明传输。将中断服务与HWI进行绑定,完成数据实时收发。运用同步模块Synchronization中的邮箱机制MBX与信号量SEM机制完成HWI、PRD和TSK之间的消息传递。运用操作系统的调度算法,完成多个任务之间的调度,控制数据收发及数据处理。

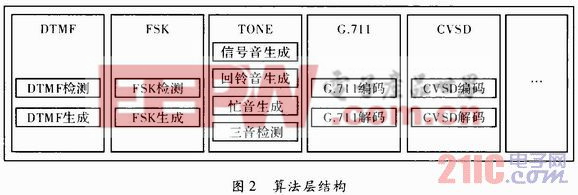

3.3 算法层

把各类算法单独列为一层,汇聚多类信号算法,采用松散耦合和可重入设计方法,方便算法的移植、维护及多路并行工作设计,并根据应用需求,方便算法的裁减和扩充。各类算法严格独立,都以单独库和头文件的形式提供。算法层的结构如图2所示。

3.4 通信常用算法

DTMF:双音多频信号,每个号码由两个音频信号相加得到,广泛用在电话拨号和来电显示中,其生成和检测算法。

FSK:利用1 200 Hz和2 200 Hz的正弦信号,采用2FSK调制解调方法,广泛用于来电显示中,其生成和检测算法。

TONE:三音生成和检测算法,包含信号音、忙音、回铃音生成和三音检测,广泛用于电话交换系统中。

G.711:速率为64 khit·s-1的语音编解码标准,广泛用于电话交换系统中。

CVSD:连续可变斜率编码的英文缩写,速率为16 khit·s-1的语音编解码标准,用于低速率通信系统中,其编解码算法。

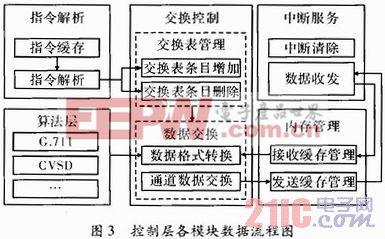

3.5 控制层

控制层设计为软件架构设计第二个关键点,在应用层与系统层、算法层之间起到桥梁作用。由指令解析、内存管理、中断服务和交换控制4个模块组成。指令解析由操作系统PRD调用,周期性的判断是否具有新的指令到来,如有新指令到来,首先把新的指令放入到指令FIFO存储器,然后清空指令空间,避免下次调用指令解析函数时做出误判断,最后指令解析模块会对指令FIFO中的内容进行解析,根据解析结果更新交换控制模块中的交换表。内存管理为每个业务通道分配了发送缓存区Tx Buffer和接收缓存区Rx Buffer,并为每个Tx Butter和Rx Buff er配备了管理指针,用于指示Buffer中的数据的存储位置及空闲位置,并由此计算出每个Buffer的数据个数及空闲空间大小,完成对异常操作如写操作过程中产生的Buffer溢出或读操作过程产生的Buffer空的处理。在产生硬件中断时,中断服务由BIOS系统HWI调用,完成实时数据收发。中断服务需要保证实时性,不作过多控制和计算,尽可能减少执行指令数目,以及使用短周期指令,必要情况下使用CCS提供的已经优化的Intrinsics函数进行程序的优化或运用汇编指令编写。HWI不可阻塞,在中断服务中,不可调用具有可能引起阻塞的函数。与系统中其他任务之间的信息交换可以通过协助模块中的邮箱机制MBX或信号灯机制SEM进行交互。交换控制模块实现不同通道数据之间的交换,并伴随不同数据格式相互转换。交换控制包含交换表管理和数据交换,具备多种的交换能力。交换表管理具有交换表条目删除和增加的功能。数据交换模块根据交换表完成源通道数据到目的通道数据格式转换,然后将转换后的数据放置到目的通道的发送缓存中,等待数据发送,具有多路并行工作能力。控制层内部模块之间的数据交互如图3所示。

3.6 应用层

应用层设计采用内存共享机制,实现DSP与CPU的指令交互和数据交互。为确保每次读写数据的完整性和正确性,两块处理器间需要建立有效的通信机制,保证不会同时对同一地址进行操作。指令交互负责接收CPU指令并向CPU返回结果。指令解析模块周期性读取指令,并进行解析,控制DSP每个业务通道的操作,如果是DTMF检测、FSK检测或TONE检测指令,DSP将解析出的结果反馈给CPU。如果是DTMF产生、FSK产生或TONE产生指令,DSP将向指定业务通道发送号码对应的DTMF信号、FSK信号或拨号音、忙音、回铃音或催挂音等;如果是两信道语音格式转换指令,DSP将从源信道接收数据,完成转换格式后,发往目的通道。数据交互,DSP与CPU通过共享内存还可进行数据交互,数据的存储状态将由内存管理模块进行控制。

4 结束语

文中介绍的软件架构,已在实际应用中得到验证,在TMS320VC5416可同时完成32路多种信号处理DTMF、FSK、TONE、CVSD、G.711任意配置,在TMS320C6418可同时完成128路多信号处理DTMF、FSK、TONE、CVSD、G.711任意配置,并可加入多路G.729处理。该软件架构能够保证不同算法的单独开发和重复利用,在跨平台移植时,根据硬件接口不同,仅需对驱动层进行重新配置,其余层的代码可直接移植,加速了多信号并行处理软件开发设计。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码