基于ADSP2106X高速并行雷达数字信号处理系统设计

2.3 集束多处理器并行系统

集束多处理器并行系统通过ADSP2106X的外部总线接口和连接口实现各处理器信息交换,如图3所示。集束多处理器并行系统可包括多个相互之间通过并行总线相连接、处理器之间相互可存取对方片内双口SRAM的子系统组成,每个子系统可包括6个处理器和一个宿主机处理器。处理器之间还可通过连接口实现点到点的通信。通常这种系统比较复杂,但它具有广泛的通用性。

3 雷达信号处理中的应用实例

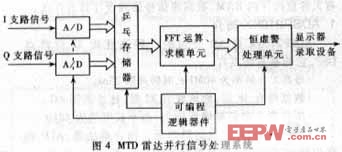

在MTD(动目标检测)雷达信号处理系统中,信号经过A/D采样后由DSP进行FFT运算,结果再作恒虚警处理,以检测动目标的有无。由以上三种典型连接方式,结合本系统的特点,进行比较:

(1)通过连接口把相邻的ADSP2106X连接在一起,构成MeshSP网格结构(图2所示)。这种结构中,每个ADSP2106X只与相邻的节点直接通信,避免了总线瓶颈,所以很适合大规模并行系统。ADSP2106X拥有6个连接口,可以组成二维或三维网格结构,但布线的难度也比较大。另外,考虑到本系统数据量大,只通过连接口传输速度太慢,故不采用这种连接方式。

(2)共享总线的多ADSP2106X系统(如图1所示),由于ADSP2106X片内具有较大容量的双口SRAM,可以省掉外接的全局存储器和各个处理器外接的局部存储器。每个处理器片内存储器既是其局部存储器,又是系统共享存储器(全局存储器)的一部分。由于每个处理器的工作程序放在其片内的双口SRAM中,因此各个处理器可真正实现并行处理。这是ADSP2106X的存储器结构所决定的,也是其它类型DSP处理器(如TMS320C40等)所不具备的优良性能。这种连接方式能达到高速传输数据的要求。但是对于本系统来说,要使用6片DSP共总线,达到了ADSP2106X共总线的极限,可能总线的驱动能力不足,故对布线提出很高的要求。

(3)为了保证系统的可靠性,决定采用共总线的同时,将连接口也相应的连接起来,增加系统的灵活性,确保系统能够完成实时处理,即采用图3所示的结构。但结合实际要求,本系统的结构框图见图4。其中FFT运算求模单元为6片ADSP2106X的集束多处理器并行结构,恒虚警处理单元为2片ADSP2106X的集束多处理器并行结构,显示录取设备为笔记本电脑。可编程逻辑器件负责控制整个系统的时序及相关逻辑。经过实际电路的测试,该系统达到了设计指标的要求。

综上所述,基于ADSP2106X并行结构的雷达信号处理系统,所需外围器件少,电路设计简单。通过对处理单元进行各种软件编程就可实现系统的功能,具有很强的扩展功能和通用性,大大缩短了研制周期,提高了系统的可靠性。这种通用结构还适用于很多高速实时处理的应用场合,具有广泛的推广应用价值。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码