基于TI达芬奇技术的高速网络摄像机设计方案

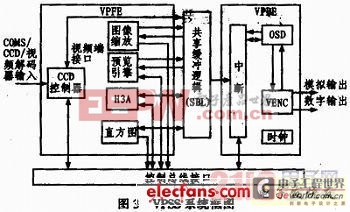

VPFE模块主要用于捕获视频信号,也可以直接从前端输入已有的视频信号。VPFE输入接口有1个CCD控制器(CCDC)、1个预处理器、柱状模块、自动曝光/白平衡/聚焦模块(H3A)和寄存器组成。CCDC可以与视频解码器、CMOS传感器或电荷耦合装置连接;预处理器是一个实时的图像处理器,它把来自CMOS或CCD的原始图像从RGB转变为YUV422的编码;柱状模块和H3A模块实现基于原始图像信息的硬件操作。

VPBE输出接口由1个OSD引擎和1个视频编码器组成。OSD引擎能够显示两组独立的视频窗口或两组独立的OSD窗口,还可以以2个视频窗口、1个OSD窗口和一个属性窗口的形式显示。OSD用于在视频图像上叠加音量,图标等位图或图像信息。视频编码模块提供数字输出和模拟输出。数字输出支持24bitRGB888格式、8/16bit BT.656以及具有独立的水平和垂直同步功能的CCIT.601输出;模拟输出支持4路10bit DAC,均工作于54 MHz,支持复合NTSC/PAL、S端子和分量视频。

3 系统硬件设计

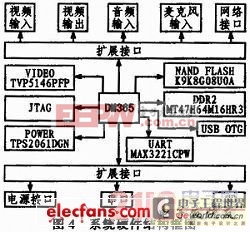

系统硬件结构如图4所示,本系统选择以TMS320DM365为嵌入式处理器,外围电路包括有音频、视频信号采集电路,以太网络电路,电源接口,JTFAG,UART,NAND Flash,SD卡,DDR2,USB2.0 OTG以及I2C。

网络摄像机系统的信息处理流程主要分为图像的获取、图像的处理传输以及图像的显示3部分。本系统中,前端摄像头负责图像的捕捉,将获取的未经压缩处理的图像信号传输至电路板中通过TMS320DM365芯片进行压缩处理以及SD卡的相应存储,再由以太网接口或其他接口将处理过图像进行传输,在远端监视器上将图像进行显示。

本系统的视频采集模块采用TVP5146。传统NTSC/PAL摄像头的输出信号格式为模拟信号,由于TMS320DM365的视频输入信号是通过VPFE的CCDC以ITU-R BT.601/BT.656格式进行输入的,所以首先需要通过视频前段滤波放大器OPA361对采集到的模拟信号进行放大,经过视频解码芯片TVPS146将模拟信号进行图像的抗混叠滤波预处理、模拟数字化转换及亮度/色度、水平/垂直同步信号的分离,实现模拟视频信号转换为数字并行信号BT.656码流格式,随后通过2个12位2选1的FET多路复用器对4路视频信号选择1路作为输入从而完成VPFE的视频输入工作。 TVP5146是一种高性能单片数字视频解码器,它可将所有常见的基带模拟视频信号,例如NTSC,PAL,SECAM混合信号数字化并解码为数字视频信号。该解码器还包括了具有模拟预处理功能的4路10位30MSPS的模数转换器。高达10组的视频输入终端可以用来配置作为RGB,YPbPr,CVBS分量信号或者S端子视频输入。

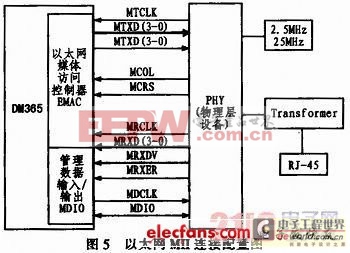

网络控制模块主要包括EMAC模块和MDIO模块,原理图如图5所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码