等离子显示器(PDP)控制电源设计与分析

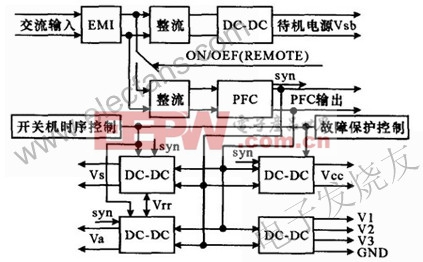

图1中的t1为PDP电源内部高低压之间的启动延时,大约为110ms,Vrr是高压封锁信号,在Vrr为高电平之后即有高压输出,图中的t3 表示Vs(165V)的软启动时间,大约为300~800ms,而Va(65V)无软启动。t4和t5仅代表关机时的先后顺序,其本身数值的大小和负载的 情况密切相关,在满载情况下t4大约为450ms,t5大约为260ms。Vs和Va变换器是一起开机、一起关机,当前两路中有1路保护(过流、过压、过 热)时,则将该两路变换器全部关断,但不关Vcc变换器。当Vcc变换器发生故障时,将Vs和Va变换器与Vcc变换器同时关断,整个电源的结构框图如图 2所示。

图2 结构框图

电路设计

为了满足PDP电源的上述特性要求,每种电源都需要不同的电路结构,下面详细论述各个电路的设计。

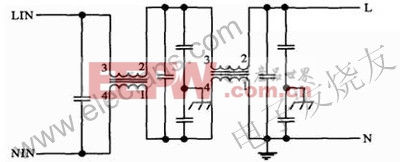

EMI电路、有源功率因数校正电路和待机电源

为了满足全球化需要,PDP电源必须满足各个组织的EMI测试要求,根据阻抗匹配采用了如图3所示拓扑结构的EMI滤波器,经过参数优化和 PCB优化,其传导辐射通过了CLASS B标准,有源功率因数校正电路采用了UC3854作为主控芯片,功率因数达到99%,待机电源采用PI公司的专用待机电源芯片构成单端反激变换器。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码