基于FPGA的光纤通信系统的设计与实现

摘要:光纤通信是现今数据通信系统的主要通信方式,其性能的好坏直接影响数据通信系统的质量。本文采用Verilog语言实现FPGA光纤通信系统的功能。光纤通信系统又包含位同步时钟提取模块、8B/10B编解码器模块和NRZI编解器模块;这些模块都利用了DA(Design Analyz er)、Quartus II以及Modelsim等EDA工具来完成综合与仿真,从仿真的结果可以看出该设计方法很好地满足了系统的要求。

关键词:光纤通信;FPGA;位同步时钟;Verilog

光纤收发器与FPGA技术相结合的方案是现在光纤通信系统的主流解决方案。目前,在超高速光纤通信中还多采用专用的ASIC芯片,但最近各FPGA厂商也相继推出了40Gbps、4x10Gbps、100Gbps和10x10Gbps等FPGA芯片,使基于FPGA超高速光纤通信的实现成为可能。FPGA的可编程特性,具有ASIC芯片无法比拟的优越性。所以基于FPGA的光纤通信有很大的现实意义。

1 光纤通信系统结构设计

光纤通信系统主要由位同步时钟提取模块、8B/10B编解码器模块和NRZI编解器模块组成.主要功能框图如图1所示。数据经8B/10编码后,能在很大程度上平衡位流中0与1的个数,而NRZI编码又做了进一步的平衡,主要是为了使信号状态变化趋于频繁以便位同步时钟提取模块更好、更快的提取出位同步时钟。编码后的信号为LVTTL电平信号,先经电平转换模块转换为PECL电平信号,再由光发送接收模块转换为光信号送入光纤传输介质。经光纤传输后,在接收端先经光发送接收模块把光信号转换为PECL电平信号,再由电平转换模块把PECL电平信号转换为LVTTL电平信号,同时位同步时钟提取模块提取出同步时钟,为解码模块提供参考时钟。最后,接收到的数据经解码后数据输出。

2 位同步时钟提取的FPGA实现

在数字通信系统中,任何消息都是通过一连串的码元序列传送的,所以接收时需要知道每个码元的起止时刻,以便在恰当的时候取样判决。这就要求接收端必须提供一个位定时脉冲序列,该序列的重复频率与码元速率相同,相位与最佳取样判决时刻一致。这种提取定时脉冲序列的过程称为位同步。同步性能的好坏直接影响通信系统的性能,出现同步误差或失去同步就会导致通信系统性能下降或通信中断。

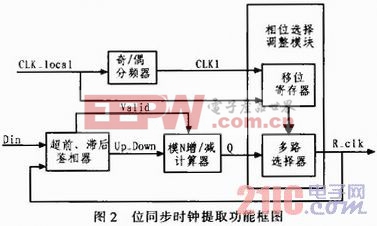

提取位同步信号有多种方法,其中最常用的是数字锁相法。其基本原理是:在接收端利用鉴相器比较接收码元和本地产生的位同步信号的相位,若两者相位不一致(超前或滞后),鉴相器就产生误差信号去调整位同步信号的相位,直至获得准确的位同步信号为止。本设计采用数字锁相法提取位同步时钟,主要由鉴相器、分频器和相位选择调整模块等几大部分组成。其功能框图如图2所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码