应对百万门级系统级芯片验证挑战的可扩展解决方案

软件模拟是模块级验证的理想选择,因为其周转速度非常迅速,纠错能力较强。硬件/软件协同验证能够将嵌入式软件带入验证流程之中,为加速处理器、记忆体以及总线运算提供途径。它也可以作为测试平台开展硬件验证。

基于处理程序的协同建模提供了大量多样化解决方案,使系统验证成为可能。协同建模适用于在高级、抽象测试平台与载入仿真器的 整个芯片的RTL实施之间建立链接。在线仿真在真实系统中提供高能力和高性能验证。仿真为设计人员带来自信,确保他们的芯片将在实际系统中正确发挥功能。

形式验证(等效性检查)的能力和速度能够确保在设计流后续阶段作出的修改不会改变其意图行为。有必要指出的是,高性能、硬件协助或软件导向解决方案对在系统级环境中实现验证完整性具有关键性作用。

各抽象层次之间的可扩展性

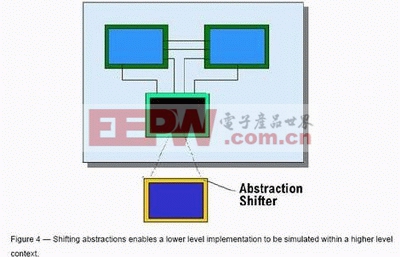

我们非常有必要推动某些方面的功能验证工作向前发展,使其成为设计流程初步阶段的一部分。为了实现这一点,我们必须利用更高层次模型和处理程序(图3)使验证工作变得更为抽象。

在设计流中前移验证的好处在于:处于这个阶段的模型的编写速度较快,具有较大生产能力,因此可以通过建设性方式影响设计决策。抽象工作可以加速验证进行,它能够剔除无关信息,缩短开发时间,加快纠错进程,并使得测试平台更易重复使用。

就复杂的系统级芯片而言,如果所有事情都在RTL或门层次上完成则太过费时和困难,我们在这儿绝对有必要在设计中使用更为抽象的表示方法。这并不仅仅是针对设计的,也同样有益于测试平台。

这种多层次抽象战略要想行之有效,不仅需要必要的工具支持,知识产权(IP)因素也同等重要。如果设计人员无法通过模型在各 个抽象层次之间切换并建立联系的话,那么多抽象模拟就无用武之地。多抽象解决方案将技术与知识产权组合在一起。针对设计的主要接口使用一系列处理程序时, 分层次验证才变得可能。它允许在各种抽象层次上混合各种设计说明。处理程序可以组合为一个测试平台或环境,用于检查某项实施是否符合高层次模型。

本策略的优势是它无需在一个抽象层次上包含所有模型。这种灵活性允许设计团队混合并匹配在规定时间内所能获得的一切,提供相对于执行时间的必要层次解析。

基于处理程序的接口可以将所有抽象系统模型链接至设计,提供一个理想的系统层次测试平台。例如,运用基于处理程序的模拟,某 团队可以在高抽象层次上作出系统定义。然后,它们将在高层次系统定义中提取某个层次或某个模块,运用处理程序投入工作所必需的知识产权,替代它们进入更为 详细的实施模型中。

他们可以在系统原位置处将模型作为即时测试平台运行。该团队就可以立即将现有测试平台投入实际使用,从而向该模块提供自然的刺激。其结果是,验证生产力提高,设计信心提高。

抽象层次

系统级验证所必需的可扩展解决方案应在整个电子系统中支持抽象:模块、子系统、完整芯片以及系统层次。

模块层次:在模块层次上,设计人员的关注重点是功能和时序的细节情况,这样他们就能够保证这些模块符合技术规范,不存在明显 问题。其目标是尽可能多地查找错误,因为这在设计流程中是查找这些错误的最廉价和最快速阶段。模拟和数字交互作用在模块层次上进行验证。功能和代码得到全 面演练,验证移交应考虑在这一阶段进行。由于HDL仿真技术易于使用且具纠错能力,因而成为理想的工具。

模拟/混合信号模 块:系统级芯片设计的能力在不断提升,模拟和混合信号元器件不断加入其中,因此要求模拟环境能够具备与数字逻辑相同的、必需的验证功能。与模拟HDL行为 模拟以及模拟原始模块的Spice模拟顺利实现接口,允许数字和模拟元器件的模拟工作实现同步,并能够在相同的纠错环境中查看。

子系统层次:所有模块均已验证后,随后进行模块集成,涉及对各模块组或整个芯片进行集成。在子系统阶段,模块间通信、控 制、时序和协议对功能而言具有重要意义;因此,检查协议或应用断言以验证总线处理程序的工具就能发挥作用。硬件断言或仿真可以运用HDL、C或 SystemC 以及Verisity等其它高层次测试平台语言布署在这一阶段。

系统级芯片层次:系统级芯片层次验证涉及各模块与后端流程的其余部分进一步集成,其中包括设计的物理实现。在设计人员将较小模块集成进入越来越大模块的过程中,需要模拟的内容日益增多,测试时间日益延长,并且需要开展更多模拟来验证设计。

这对多种验证方法提出了要求,比如芯片和系统功能测试。它还要求验证布图、时钟树或DFT插入会否引入意外更改。等效性检查工具可以验证整个大规模设计,并在每次修改设计后迅速纠错,无需再运行众多漫长的模拟。

除了等效性检查之外,我们还可能在这一流程中使用硬件加速仿真器和多CPU并行仿真,以确保更改设计期间没有造成任何破坏。 多CPU并行仿真将会缩短测试时间,获得非常高的吞吐能力。就较长时间测试而言,出于验证大规模芯片设计的能力考虑,硬件仿真是我们的首选方法。硬件加速 仿真器和多CPU并行仿真是互为补充的解决方案,可以在不同的环境中得到有效使用。

绝大多数系统级芯片器件都包含必须验证的嵌入式软件,其中包括应用代码、实时操作系统(RTOS)、器件驱动程序、硬件诊断以及启动ROM代码。功能仍然重要,但吞吐能力以及其它系统级事宜可能也需要获得验证。运行大量软件通常意味着长时间模拟作业。

硬件/软件协同仿真解决方案提供降低总体负担的途径,同时也提供高效能纠错和分析环境。即便就较长运行时间而言,该设计可能也需要部分或全部移入硬件解决方案之中,但应该保留相同或相当的纠错环境,这样就可以最大限度减少上述执行环境中的迁移。

改进的纠错解决方案

为支持可扩展验证解决方案,纠错工具必须实现集成,在各个抽象层次上保持前后一致,在各个可扩展性工具之间保持一致。其目标 是加快速度发现错误、跟踪捕获故障原因、修复故障,并最大限度缩短反馈时间,将反复回路减少到最低限度。目前,无论是设计团队还是验证团队,都将超过 50%的时间用在纠错上,因此这一领域的改进可能对缩短产品上市时间产生重大影响。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码