多维设计技术力促3D芯片

您可能听说过这样的宣传:随着目前还是平面结构的裸片向多层结构的过渡,半导体制造基础在今后几年内将发生重大转变。为了使这种多层结构具有可制造性,全球主要半导体组织作出了近10年的不懈努力,从明年开始三维(3D)IC将正式开始商用化生产——比原计划落后了好几年。

芯片制造商用了好几年时间才使得用于互连3DIC的硅通孔(TSV)技术逐渐成熟。虽然硅通孔技术一直用于2D任务,比如将数据从平面芯片的前面传送到反面的凸块,但使用堆叠裸片的3DIC已经排上议事日程。

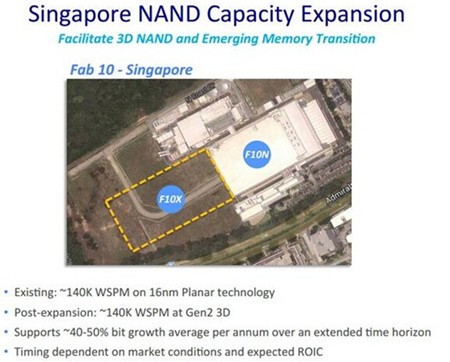

去年举行的国际固态电路会议主要讨论的内容是“近似3D”芯片,如三星公开宣扬的1Gbit移动DRAM(计划到2013年跃升至4Gbit)。三星的这种2.5D技术非常适合位于系统级芯片之上且带硅通孔和微凸块的堆叠式DRAM裸片。

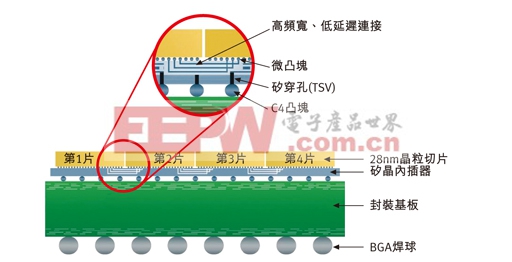

今年秋季则迎来第二个重大的2.5D成功事件,赛灵思公司推出一种使用某封装工艺的多FPGA解决方案,这种工艺可在硅中介层上互连4个并排且带微凸块的Virtex-7FPGA。台湾的台积电(TSMC)公司正在生产这种硅中介层,该中介层使用硅通孔技术重新分配FPGA的互连,而硅通孔则匹配使用受控塌陷芯片连接(C4)的基板封装上的铜球。台积电公司承诺明年将向其它代工客户提供其开创性的2.5D至3D转换技术。

然而,2011年令人惊讶的3DIC发布来自IBM。据IBM公司最近透露,公司正在秘密地大批量生产大众化移动消费设备使用的成熟3DIC产品,尽管使用的是低密度硅通孔技术。作为收获的经验之谈,IBM声称现在已经认识到3D芯片制造中的遗留工程技术问题,并表示有望在2012年解决这些问题。

“拥有一技之长的年代已经过去。”IBM公司研究副总裁BernardMeyerson表示,“如果您仅依靠材料,或芯片架构,或网络架构,或软件和集成,您就可能无法赢得3D性能战争。要想打赢这场战争,您需要以尽可能最全面的角度使用所有这些资源。”

近期,IBM宣布联合3M公司并开始研讨创建设计师材料——就像是Meyerson描述的寻找“一个真正高的矮人”——这种材料将解决3DIC生产中面临的最终工程技术问题:过热。3M的任务是创建一种适合堆叠裸片间使用的底部填充材料,这是一种电气绝缘材料(像电介质),但导热性比硅要好(像金属)。3M公司承诺在两年内实现这种神奇材料的商用化。

“现在我们正在做试验,到2013年我们希望开始广泛的商用。”3M公司电子市场材料事业部技术总监陈明(音译)表示。

一些分析师不认为IBM-3M联合研发努力会使他们的产品在3DIC领域中走得比别人更远。

“3M正在研制的底部填充材料将解决3D堆叠中遇到的散热问题。”MEMS投资者杂志高级封装技术首席分析师FrancoisevonTrapp表示,“虽然在大批量生产3DIC之前肯定需要解决遗留下来的一些限制,但我认为任何人都不会相信这是解决3D堆叠遗留问题的终极方案。”

3D无处不在

即使IBM宣称的领先的3DIC生产技术也不是没有挑战者。事实上,TezzaronSemiconductor公司为其钨硅通孔工艺提供3DIC设计服务已经有多年时间了。Tezzaron的FaStack工艺可以从薄至12微米晶圆上的异质裸片创建3D芯片。这种工艺具有针对堆叠式DRAM的宽I/O特性,而且其亚微米互连密度高达每平方毫米100万个硅通孔。

去年获得EETimes年度ACE创新大奖的ZviOr-Bach则认为3DIC设计师需要从硅通过技术过渡到超高密度的单片3D技术。对Or-Bach来说这个观点一点都不令人奇怪,因为他最近的角色是IP开发公司MonolithIC3DInc的总裁兼首席执行官。而BeSangInc等新创企业声称正在制造无硅通孔的单片3D内存芯片原型,并有望于2012年首次亮相。

然而,目前最先进的技术应该是使用硅通孔的3D芯片堆叠,而且每家主要的半导体公司都在研究这种技术。“IBM将这种技术发挥至了极致,并突破传统思维与3M公司开展合作。然而,IBM公司在3D领域做出的每次进步都将激发三星、Intel和台积电等竞争对手的创造性,所有这些公司都在独立开发3DIC技术。”市场观察人士、TheEnvisioneeringGroup总监RichardDoherty指出。

生产3DIC的技术并不是很新的技术,目前的工作专注于进一步完善。举例来说,现在许多CMOS成像器使用硅通孔将像素数据从前面带到基板后面,而堆叠芯片想法本身可以追溯到大约1958年颁发给晶体管先驱WilliamShockley的早期专利。从那以后,业界已经使用了许多堆叠式裸片配置——例如,将MEMS传感器堆叠在ASIC之上,或将小的DRAM堆叠在处理器内核上——但通常是使用绑定线实现互连。

从绑定线转变到硅通孔能使互连密度更高,还能帮助设计师脱离矩形的“农场地”框框的束缚,使他们在设计芯片版图时更像是在设计电路板。没有电路的区域可以用于其它结构,例如垂直互连总线甚至用于冷空气的烟道。异质3D堆叠式裸片还能达到新的集成度,因为整个系统可以组合成单个硅块。

“3DIC带来的最重要影响是远离农场式设计的机会,这种农场式设计是将每个芯片分割成相邻且完全拼接式的矩形块。”Doherty指出,“与用光芯片上的所有面积不同,3D芯片设计师可以从裸片上切割出方形、三角形和圆形进行垂直互连,并很好地释放出热量。”

“3D技术可以给芯片设计带来许多新的想法。设计师必须采用不同的思维方式,以创新的方式组合他们的CPU、内存和I/O功能,这是每样东西只能在邮票大小的面积上并排放置的方法所不能做到的。”

有许多半导体协会都在研究制订3D技术标准。国际半导体设备与材料组织(SEMI)有4个小组专攻3DIC标准。其三维堆叠式集成电路标准委员会包括SEMI成员Globalfoundries、惠普、IBM、Intel三星和UnitedMicroelectronicsCorp.(UMC)以及Amkor、ASE、欧洲的校际微电子中心(IMEC)、亚洲的工业技术研究院(ITRI)、奥林巴斯、高通、Semilab、东京电子和赛灵思公司。

图1:赛灵思公司组合运用硅通孔和受控塌陷芯片连接焊球在台积电生产的硅中介层上安装4个FPGA。(图片来源:赛灵思)

更多资讯请关注:21ic模拟频道

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码