全集成设计环境下的视频处理系统开发简介

通常,视频处理系统的实现需要支持各种视频和音频标准,并负责把信号从一种标准转换到另一种标准。多媒体应用要求以视频速率处理信号,这意味着在开发过程中仿真必须实时运行。

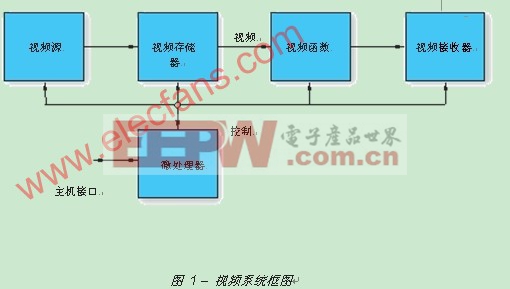

典型的视频处理系统使用一个微处理器来控制一个视频流水线,该视频流水线包括一个视频源和宿,一个用于存储视频数据的大型存储器,和一个视频处理系统(图 1)。

在实现和调试各种视频算法时,您需要通过软件和硬件仿真来验证其功能性。视频流的实时特性和每帧所需的大量视频数据,令视频处理应用的仿真产生了特别的挑战。

设计环境

视频基本套件(VSK) 支持广泛视频应用领域的高性能视频处理系统的快速开发与调试。VSK 采用赛灵思?Virtex-4 XC4VSX35 器件,该器件通过结构中高比例的乘法累加块(也称为 DSP48)而针对 DSP 处理进行了优化,并具有丰富的视频接口特性集支持,如 DVI、VGA、分量(HD)、复合、S视频和 SDI等。

通常,开发视频算法需要使用硬件对实时数据流进行视频操作验证,需要仿真环境来开发和测试视频处理组件。VSK 为视频系统的每个组件同时提供了软件仿真和实时操作,可让您开发视频 IP(包括滤波器、视频块集、加速器和视频接口转换)或最终应用程序,如编解码器、图像增强、动态伽马校正和运动估计等。与工具套件的集成和 I/O 多样性使能快捷而容易地把视频引入板上和优化其运行算法。

与 VSK 一起提供的还有参考设计,其中一些使用 HDL 编写,其他的则用Xilinx System Generator for DSP 设计环境构建。为了去除通过各种视频接口引入数据并把它们发送到 Virtex-4 器件的复杂性,所以我们附带了一个视频接口块集库,使所有接口块集均可通过一个 MicroBlaze控制器来进行控制。

为了突出显示 VSK 的部分能力,我将对 MPEG-4 第 2 部分解码器演示设计进行说明。

MPEG-4 第 2 部分

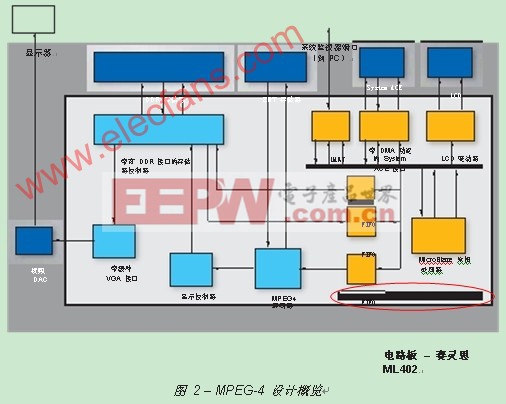

该 MPEG-4 解码器演示系统由 FPGA 硬件评估平台、赛灵思 IP 核和嵌入式软件组成,并一起对工业标准编码视频位流执行解压操作。

对于此设计,FPGA 被编程为执行解压和驱动视频显示之用。一个 Compact Flash 卡用于保存多个压缩视频流和 FPGA 配置位流。一个位于 FPGA 内的嵌入式处理器从 Compact Flash 卡读取位流,将其写入一个外部 DDR 存储器中,然后将其发送到 MPEG-4 第 2 部分解码器。然后通过视频 I/O 子卡,将解码器的输出重新格式化为要在外部监视器上显示的视频标准。

系统概览如图 2 所示。MPEG-4 解码器核、DDR 存储器控制器、颜色空间转换器、VGA 接口、宏块格式转换器、以及 MicroBlaze 软核处理器及相关外围电路,在 XC4VSX35 FPGA 中实现。而ZBT 存储器、DDR 存储器、System ACE技术、Compact Flash 连接器、两线式 LCD 显示器,和一个数模转换器,都是位于硬件平台上。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码