基于FPGA的NCO设计方案

4 设计实现及其仿真波形

本次设计采用性价比较高的ALTERA 公司的STRATIX芯片进行设计仿真,该系列芯片是基于1.5 V 工作电压、0.13 μm全铜布线SRAM 工艺的FPGA 芯片。此系列芯片拥有最多114 140 个逻辑单元(Les)和最多10 Mbits 的内部RAM.该系列芯片支持多种I/O 标准,提供了最多可达12 个的用于处理复杂时钟信号的锁相环(PLLs)。同时,STRATIX 系列芯片提供了最多可达28 个的数字信号处理单元(DSP),它们由总共224 个内置硬件乘法器(9 位乘9 位)组成,利用它们可以有效地实现例如快速傅立叶变换(FFT)、有限冲击响应(FIR)滤波器、无限冲击响应(IIR)滤波器等高性能的数字信号处理单元或者乘法器。

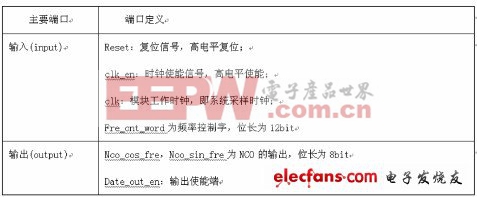

图3 NCO 模块的主要端口定义

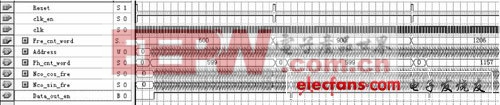

2)Quartus 仿真输出波形,如图4 所示。

图4 NCO 的仿真输出波形

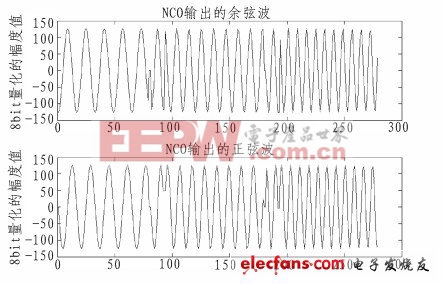

此仿真波形为3 个频点的NCO 输出波形, 用matlab 绘出输出的载波的波形如图5 所示。

图5 输出载波的波形

由上面的仿真结果可以看出,NCO 正确输出了3 个频点的仿真波形;同时通过实际的FPGA 硬件测试和验证,该设计达到了所要求的性能指标。

5 资源占用情况

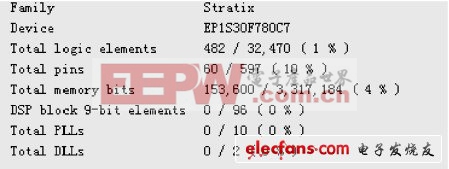

使用Altera 公司的STRATIX 芯片进行编译、综合,所得的资源占用结果如图6 所示。

图6 NCO 资源占用情况

6 结束语

本文给出了一种基于FPGA 的正交NCO 的设计方法,在实际应用过程中可参考给出的设计实例,通过改变频率控制字、系统采样频率、存储正余弦查找表的深度和存储表的位宽,即可得到不同输入频率范围的NCO;同时如果涉及需要的精度及频率较高, 也可采用外置的存储器, 如FLASH,SRAM 等与FPGA 配合使用, 较大的扩展存储表的深度和位宽,可最终达到设计的要求。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码