基于FPGA的卷积码编译码器

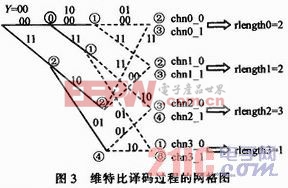

其中“比前路径长度”中下划线前的数字代表该路径最后停在的状态,下划线后的数字代表是由哪个状态转移过来的。如果是“0”则代表由状态号较小的状态转移过来的那条路径,反之如果为“1”则代表由状态号较大的状态转移过来的那条路径;“选后路径长度”和“译码路径”的序号表示该路径最后停在的状态号。图3为维特比译码过程的网格图。

2.3.2 定时与控制

由时钟控制,每个时钟输入一位,每两个时钟输出一位,称为一个译码周期。在每个译码周期的前一个时钟周期内完成“加”,此时译码状态为“0”;在后一个时钟周期内完成“比和选”,译码状态为“1”。

2.3.3 支路量度计算

由于(2,1,3)卷积码的形式已经固定,因此,可以事先把支路量度表做好,如表1所示。译码器工作时可根据输入通过查表得到“比前路径长度”的增加值,暂存到addi_j中,而后统一加入“比前路径长度”chni_j中。

2.3.4 路径量度和译码路径的更新与存储

在到达同一状态的两条路径中选取路径长度较小的作为幸存路径,即在chnk_0和chnk_1中选择较小的存入rlengthk(k=0~3)。

由于每个状态译码路径的最后一位在每一步中是不变的,均是0101”(状态0~3),因此更新译码路径时只需将选中的译码路径向高位移一位后存储即可。即进行如下判断:

1)对于新路径0的判断,如果chn0_0=chn0_1则选择旧路径0,否则选择旧路径2;

2)对于新路径1的判断,如果chn1_0=chn1_1则选择旧路径0,否则选择旧路径2;

3)对于新路径2的判断,如果chn2_0=chn2_1则选择旧路径1,否则选择旧路径3;

4)对于新路径3的判断,如果chn3_0=chn3_1则选择旧路径1,否则选择旧路径3;

其中chn0_0,chn0_1,chn1_0,chn1_l,chn2_0,chn2_1,chn3_0,chn3_1已由上一步得出。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码