IBIS 模型:利用 IBIS 模型研究信号完整性问题

集总式电路与分布式电路对比

传输线一经定义,下一个步骤便是确定电路布局代表集总式系统还是分布式系统。一般而言,集总式系统体积较小,而分布式电路则要求更多的板空间。小型电路具备有效的长度 (LENGTH),其在信号方面比最快速电气特性要小。要成为合格的集总式系统,PCB 上的电路必须要满足如下要求: (5)

(5)

其中,tRise 为以秒为单位的上升时间。

在 PCB 上实施一个集总式电路以后,端接策略便不是问题了。根本上而言,我们假设传送至传输导线中的驱动器信号瞬间到达接收机。

IBIS 模型的数据组织结构

根据 IC 的电源电压范围,一个 IBIS 模型包括三、六或者九个角的数据。决定这些角的变量为硅工艺1、电源电压和结温。某个器件模型的具体工艺/电压/温度 (PVT) SPICE角对创建精确的 IBIS 模型至关重要。额定值不同,硅工艺也各异,创建的模型也有弱有强。设计人员根据组件的电源要求定义电压设置,并让其在额定值、最小值和最大值之间变化。最后,根据组件的指定温度范围、额定功耗和封装的结点到环境热阻,即 θJA,来确定组件硅结点的温度设置。

表1列举了一个例子,其为三 PVT 变量及其与 TI 24 位生物电势测量 ADC ADS129x 系列的 CMOS 工艺关系。这些变量用于实施六次SPICE模拟。第一次和第四次模拟均使用额定工艺模型、额定电源电压和室温条件下的结点温度。第二次和第五次模拟均使用弱工艺模型,低电源电压和高结温。第三次和第六次模拟使用强工艺模型、更高的电源电压和更低的结温。PVT值之间的关系映射CMOS工艺的最佳角。

表 1 ADS1296 IBIS 模型的 PVT 模拟角

角数 | 硅工艺 | 电源电压(V) | 温度(°C) |

1 | 额定 | 1.8 | 27 |

2 | 弱 | 1.65 | 85 |

3 | 强 | 2.0 | -40 |

4 | 额定 | 3.3 | 27 |

5 | 弱 | 3.0 | 85 |

6 | 强 | 3.6 | -40 |

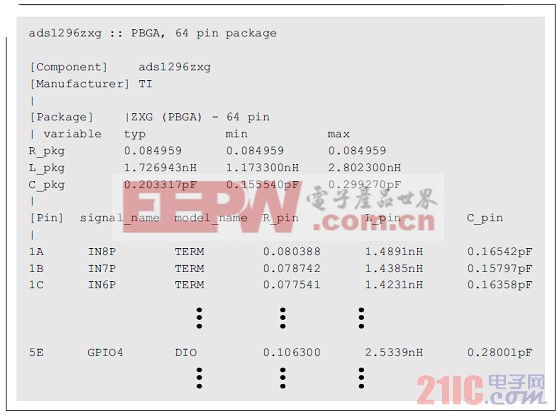

信号完整性评估的规定发送器规范包括输出阻抗 (ZT) 和升降时间(分别为tRise和 tFall)。图 5 显示了列举自 IBIS 模型文件的 TI ADS1296 封装ads129x.ibs。5用于产生阻抗的值显示在“[Pin]”关键字下面,其也位于缓冲模型(未显示)中。升降时间位于 IBIS 模型数据列表的瞬态部分。

图 5 ADS1296的IBIS 模型封装列表,包括 L_pin 和 C_pin 值

输入和输出引脚的阻抗

任何信号的引脚阻抗均由加至模型阻抗的封装电感和电容组成。图 5 中,关键字“[Component]”、“[Manufacturer]”和“[Package]”描述了一个具体的封装,即64引脚PBGA(ZXG)。具体引脚的封装电感和电容可在“[Pin]”关键字下面找到。例如,在引脚 5E 处,信号 GPIO4,可找到 L_pin 和 C_pin 值。该信号和封装的 L_pin(引脚电感)和 C_pin(引脚电容)值为 1.4891 nH 和 0.28001 pF。

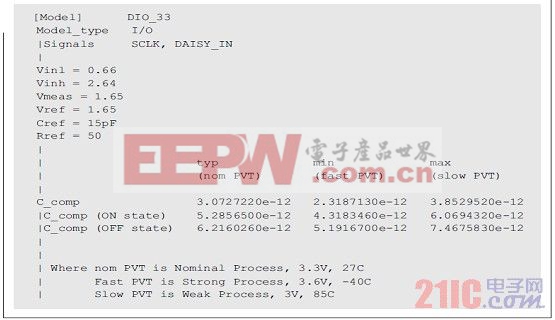

第二个重要的电容值为硅电容,即C_comp。C_comp值可在 ads129x.ibs 文件的模型 DIO_33 列表中的“[Model]”关键字下面找到(参见图 6)。该模型中的C_comp 为 DIO 缓冲器的电容,其电源引脚电压为 3.3V。“|”符号表示注释;因此,该列表的有效C_comp值为3.0727220e-12 F(典型值)、2.3187130e-12 F(最小值)和 3.8529520e-12 F(最大值),PCB 设计人员可从中选取。在 PCB传输线设计阶段,3.072722 pF 典型值为正确的选择。

图 6 ads129x.ibs 文件 C_comp 值模型 DIO_33 列表

图 7 端接-校正策略

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码