全加器功能及应用的仿真设计分析

采用同样的方法,将全加器本位和Si的真值表写入逻辑转换仪,操作逻辑转换仪相应的图标,可以准确地得到全加器本位和Si的标准与或表达式或最简与或表达式,

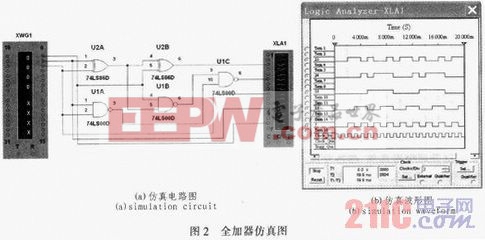

通过逻辑转换仪设计出全加器的功能,进行仿真测试,如图2所示。是根据设计得到逻辑表达式或逻辑图,按照最简仿真电路图图2(a),利用Multisim仿真软件中字信号发生器XWG(Word Generator,又称数字逻辑信号源)这个能产生32路(位)同步逻辑信号的仪器,用来对数字逻辑电路进行测试。XWG1产生全加器3个输入变量的二进制逻辑组合。使用时,对字信号发生器面板上的各个选项和参数进行适当设置,才能使其正常工作和显示。全加器仿真测试时参数设计地址为0000~0007、控制按循环输出及逐个加1递增方式编码、选择内部触发方式、输出频率为1 kHz,作为电路信号。逻辑分析仪XIA(Logic Analyzer)可以同步记录和显示16路逻辑信号,用于对数字逻辑信号进行高速采集和时序分析。XLA1测试全加器输入输出的仿真波形,如图2(b)所示,图中波形从上至下分别是全加器输出和Si、进位Ci、输入Ai、Bi及低位进位Ci-1。从对应关系上观察分析实际结果与理论设计相吻合,而且无竞争和冒险现象产生。从输入变量波形的对应关系可见,字信号发生器XWG的输出,随着输出端子号的增加频率按照二分频在衰减,如图2(b)所示,每增加一个输出端,频率就衰减二分之一。所以在使用XWG时,输入的对应关系一定要准确,否则就仿真不出结果。

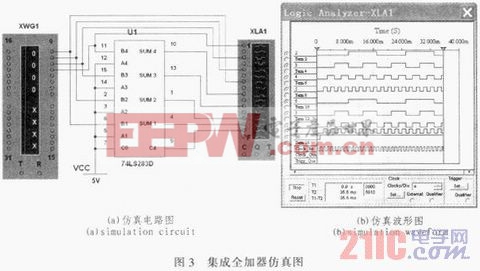

3.2 集成全加器仿真分析

在实际应用中广泛采用的是集成全加器,代号74LS283。它是一个四位全加器,可以实现四位加法运算和功能扩展应用。全加器74LS283功能仿真电路如图3(a)所示。为了能够监测判断出集成芯片的完好状态,将两个加数中的一个及低位进位均设置为高电平“1”接电源VCC,这样全加器输出的和就应该与另一个加数完全相同,仿真结果如图3(b)所示。图中从上至下分别显示的波形是加数B4、B3、B2、B1,本位和S4、S3、S2、S1,最高位进位C4。仿真测试时字信号发生器参数设计地址从0000~000F,其余设置同上。图3结果表明全加器74LS283的芯

片完好,功能准确。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码