JPEG2000中53离散小波多层变换FPGA实现研究

3.2 地址生成模块的设计

对于做三层的离散小波变换,每层对RAM的(行/列)读/写地址都不相同,所以在地址生成模块中分别做了三层各自的地址模块,每个单层地址模块产生2路读地址信号、2路写地址信号和1路写地址使能信号。首先产生行变换的读/写地址,在行变换完成之后产生列变换的读/写地址,在列变换完成之后,给出一个EndOfBlock信号返回给图4中的Control模块。由Control模块控制分层地址模块的使能以及Select模块选择有效地址信号输出,并且通过对读地址计算算法的调度,实现分裂和边界延拓功能,不需要另外设计单独的处理模块,地址生成模块的总体框图如图4所示。

4.功能仿真及FPGA测试验证

该设计采用了流水线技术即通过插入寄存器,使得一组输入数据的计算分布在同一个时钟周期中,从而提高资源利用率,增加电路的数据处理量,提高了性能,在此用Verilog HDL描述实现。

4.1 功能仿真

在ModelSim的测试模块中设置时钟为100 MHz,图5为部分仿真结果,输入数据在经过3个时钟周期后计算出LH分量输出。由此可见,一维小波变换模块的设计符合JPEG 2000标准规定,结果正确。

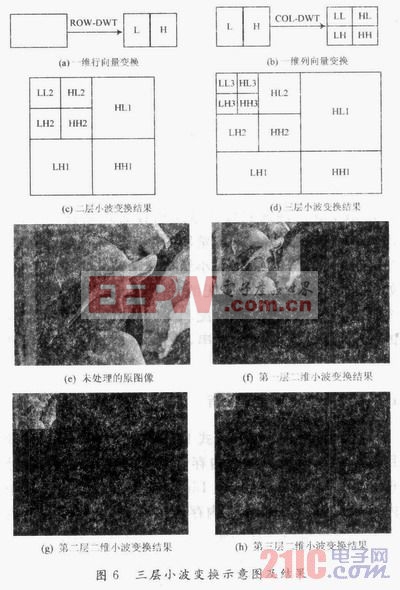

二维小波变换结果就是,在行变换结束之后对于行方向上面的LH分量再做列方向上的小波变换,得到LL,HL,LH,HH分量,对于多层小波变换就是在前一层变换的结果上对LL子带再进行二维DWT变换,多层小波变换的示意图如图6所示。

4.2 FPGA测试验证

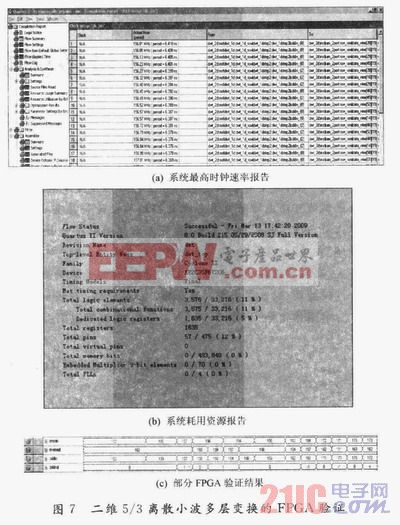

该设计的FPGA验证采用Altera的DE2开发板平台,开发板采用CycloneⅡEP2C35作为主FPGA芯片,具有丰富的I/O接口与显示存储设备,可以满足该设计的验证工作。

本次FPGA的验证中使用Altera的SignalTapⅡ嵌入式逻辑分析仪。SignalTapⅡ嵌入式逻辑分析仪集成到QuartusⅡ设计软件中,能够捕获和显示设计中实时信号的状态,这样开发者就可以在整个设计过程中以系统级速度观察硬件和软件的交互作用。它支持多达1 024个通道,采样深度达128 Kb,每个分析仪均有10级触发输入/输出,使用SignalTapⅡ无需额外的逻辑分析设备,只需将一根JTAG接口的下载电缆连接到要调试的FPGA器件即可。

下载验证结果如图7所示,整个系统时钟可以达到156 MHz,速度很快,耗用资源相对较少,运算结果正确。

5 结语

本文提出了一种快速、有效的JPEG 2000 5/3小波变换的VLSI设计结构,该结构将数据的奇偶分裂、边界延拓嵌入到地址产生单元对双端口RAM的操作中,不需要额外的计算单元,采用移位-相加操作代替卷积操作,通过Verilog编写RTL级代码并进行功能仿真,最后完成了在FPGA上的验证,最高时钟频率达到156 MHz,整体性能优越。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码