一种低压低功耗衬底驱动轨至轨运算放大器设计

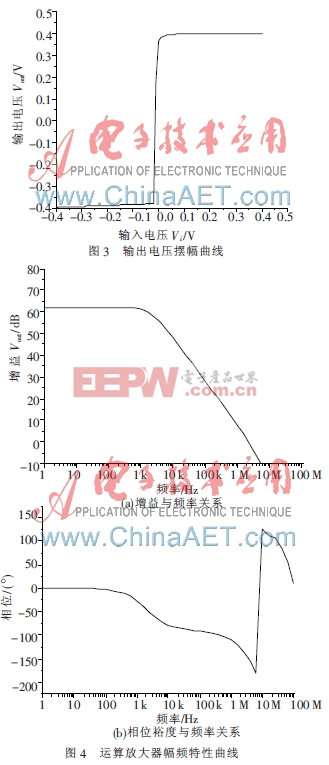

将该运算放大器接成闭环形式,反向增益为10,测量其输出电压范围,所得输出电压摆幅曲线如图3所示。从图中可以看到,输出电压摆幅约为-0.39 V~0.395 V时,基本达到轨至轨输出。至此,运算放大器已达到了轨至轨输入和轨至轨输出的设计要求。

图4为运算放大器的幅频特性曲线。当电源电压取0.8 V时,得到直流开环增益为62.1 dB,单位增益带宽2.14 MHz,相位裕度52°,功耗为65.9 μW。

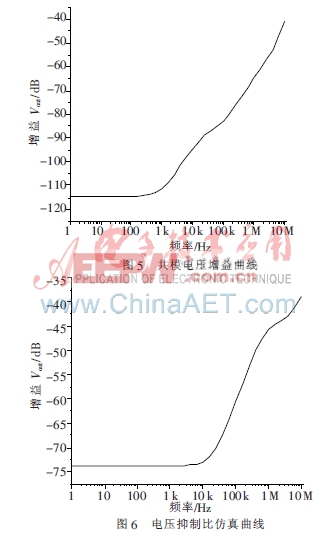

在运算放大器的两个输入端加相同的信号,做交流小信号分析,测出电路的共模电压增益如图5所示。在低频下,电路的共模增益为-114 dB,结合前面交流小信号分析的结果,可得出电路的共模抑制比为176.1 dB。图6为电压抑制比仿真曲线,低频时,电压抑制比约为-73.8 dB。

综上仿真结果表明,该衬底驱动运算放大器具有良好的性能。虽然运算放大器的频率带宽和线性度有所下降,但是却能有效避开阈值电压的限制,将电源电压降低到0.8 V,功耗为65.9 μW,同时实现了轨至轨的输入/输出电压范围。

在传统的栅驱动轨至轨运算放大器信号通路中存在MOS管阈值电压的影响,因此限制了其在超低电源电压下的应用。本文通过采用衬底驱动互补差分对电路,有效降低了CMOS模拟集成电路对电源电压的要求,通过改进型前馈式AB类输出级来提高电压的增益,实现了超低压下运算放大器信号放大,获得了-0.36 V~0.39 V的共模输入范围和-0.39 V~0.395 V的输出电压范围。仿真得到该运算放大器具有良好的性能指标,能够有效地驱动阻性负载,且结构简单,适于低压低功耗模拟集成电路应用。

参考文献

[1] 肖明,吴玉广,董大伟.基于准浮栅的低功耗差分运算放大器[J].微计算机信息,2007,23(2-2):286-287.

[2] 张海军,朱樟明,杨银堂,等.一种基于衬底驱动技术的0.8V高性能CMOS OTA[J].电子器件,2006,29(2):344-347.

[3] 邓红辉,尹勇生,高明伦.1.5 V低功耗CMOS恒跨导轨对轨运算放大器[J].科技导报,2009,27(23):57-61.

[4] LAYTON K D, COMER D T, COMER D J. Bulk-driven gain-enhanced fully-differential amplifier for VT+2Vdsat operation[J]. Circuits and Systems, 2008, 18:77-80.

[5] 杨银堂,李娅妮,朱樟明.一种0.8 V衬底驱动轨对轨运算放大器设计[J].固体电子学研究与进展,2009.29(3):344-347.

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码